Η διαδικασία σχεδιασμού του ψηφιακού υλικού έχει αλλάξει έντονα τα τελευταία χρόνια. Έτσι, μικρά ψηφιακά κυκλώματα μπορούν να εφαρμοστούν χρησιμοποιώντας PAL και PLA. Κάθε συσκευή χρησιμοποιείται για την εφαρμογή διαφόρων κυκλωμάτων που δεν χρειάζονται περισσότερο από τον αριθμό των όρων i / ps, o / ps και προϊόντων που προσφέρονται στο συγκεκριμένο chip. Αυτά τα τσιπ είναι ανεπαρκή σε αρκετά μέτρια μεγέθη, υποστηρίζοντας κανονικά έναν αμοιβαίο αριθμό εισόδων και εξόδων που δεν υπερβαίνουν τα 32. Για το σχεδιασμό αυτών των κυκλωμάτων που χρειάζονται περισσότερες εισόδους και εξόδους, μπορούν να χρησιμοποιηθούν πολυάριθμα PLA / PAL ή αλλιώς ένας πιο αριστοκρατικός τύπος του chip μπορεί να χρησιμοποιηθεί που ονομάζεται CPLD (σύνθετη προγραμματιζόμενη λογική συσκευή). Ένα τσιπ CPLD περιλαμβάνει πολλά μπλοκ κυκλώματος σε ένα μόνο τσιπ με πόρους εσωτερικής καλωδίωσης για να συνδέσετε τα μπλοκ κυκλώματος. Κάθε μπλοκ κυκλώματος είναι συγκρίσιμο με ένα PLA ή PAL.

Τι είναι μια σύνθετη προγραμματιζόμενη λογική συσκευή;

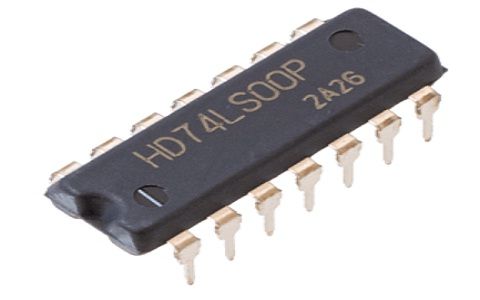

Το ακρωνύμιο του CPLD είναι «Σύνθετες προγραμματιζόμενες λογικές συσκευές», είναι ένα είδος ολοκληρωμένου κυκλώματος ότι οι σχεδιαστές εφαρμογών σχεδιάζουν να εφαρμόζουν ψηφιακό υλικό όπως τα κινητά τηλέφωνα. Αυτά μπορούν να χειριστούν εν γνώσει υψηλότερα σχέδια από τα SPLD (απλές προγραμματιζόμενες συσκευές λογικής), αλλά προσφέρουν λιγότερη λογική από τα FPGAs ( προγραμματιζόμενες συστοιχίες πύλης πεδίου ). Τα CPLD περιλαμβάνουν πολλά λογικά μπλοκ, καθένα από τα μπλοκ περιλαμβάνει 8-16 μακροκύτταρα. Επειδή κάθε λογικό μπλοκ εκτελεί μια συγκεκριμένη λειτουργία, όλα τα μακροκύτταρα σε ένα λογικό μπλοκ είναι πλήρως συνδεδεμένα. Ανάλογα με τη χρήση, αυτά τα μπλοκ ενδέχεται να συνδέονται ή όχι μεταξύ τους.

Σύνθετη προγραμματιζόμενη λογική συσκευή

Τα περισσότερα CPLD (σύνθετες προγραμματιζόμενες λογικές συσκευές) έχουν μακροκύτταρα με ένα άθροισμα λογικής λειτουργίας και μια επιλογή FF (flip-flop) . Ανάλογα με το τσιπ, η συνδυαστική λειτουργία λογικής υποστηρίζει από 4 έως 16 όρους προϊόντος με ενσωματωμένο fan-in. Τα CPLD διαφέρουν επίσης από την άποψη των καταχωρητών βάρδιας και των λογικών πυλών. Λόγω αυτού του λόγου, μπορούν να χρησιμοποιηθούν CPLD με τεράστιο αριθμό λογικών πυλών αντί για FPGA. Μια άλλη προδιαγραφή CPLD δηλώνει τον αριθμό των όρων προϊόντος που μπορεί να επιτύχει ένα μακροκύτταρο. Οι όροι προϊόντων είναι το προϊόν ψηφιακών σημάτων που εκτελούν μια συγκεκριμένη λογική λειτουργία.

Τα CPLD είναι διαθέσιμα σε διάφορες φόρμες πακέτων IC και σε λογικές οικογένειες. Τα CPLD διαφέρουν επίσης ως προς την τάση τροφοδοσίας, το ρεύμα λειτουργίας, το ρεύμα αναμονής και την απόρριψη ισχύος. Επιπλέον, αυτά διατίθενται με διάφορες ποσότητες μνήμης και διάφορα είδη υποστήριξης μνήμης. Συνήθως, η μνήμη εκφράζεται σε bit / megabit. Η υποστήριξη μνήμης αποτελείται από ROM, RAM και διπλή θύρα RAM. Περιλαμβάνει επίσης μνήμη CAM (περιεχόμενο που μπορεί να αντιμετωπιστεί), καθώς και μνήμη FIFO (πρώτη-πρώτη, πρώτη-έξοδος) και μνήμη LIFO (τελευταία-τελευταία, τελευταία-έξω).

Αρχιτεκτονική σύνθετης προγραμματιζόμενης λογικής συσκευής

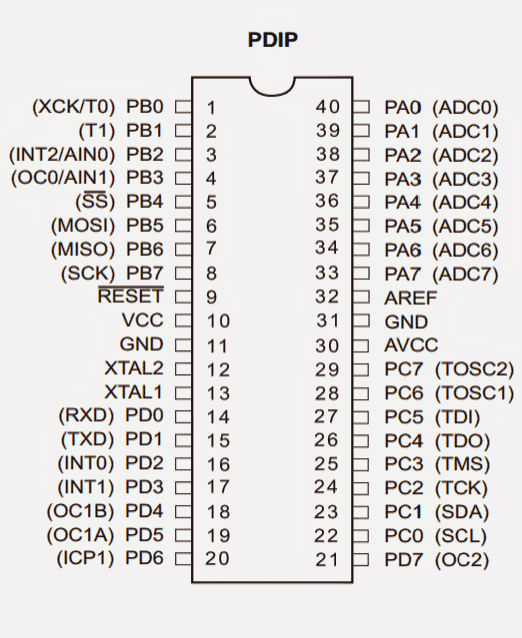

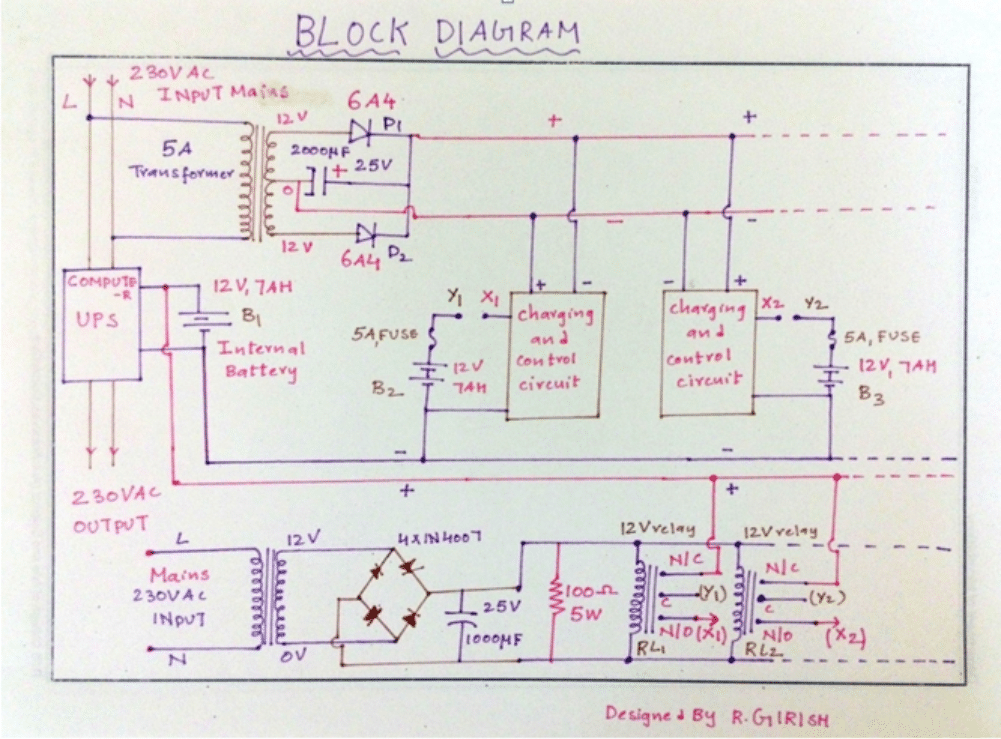

Μια πολύπλοκη προγραμματιζόμενη λογική συσκευή αποτελείται από μια ομάδα προγραμματιζόμενων FB (λειτουργικά μπλοκ). Οι είσοδοι και οι έξοδοι αυτών των λειτουργικών μπλοκ συνδέονται μεταξύ τους με ένα GIM (παγκόσμιος πίνακας διασύνδεσης). Αυτή η μήτρα διασύνδεσης είναι αναδιαμορφώσιμη, έτσι ώστε να μπορούμε να τροποποιήσουμε τις επαφές μεταξύ των λειτουργικών μπλοκ. Θα υπάρξουν κάποια μπλοκ εισόδου και εξόδου που μας επιτρέπουν να ενώσουμε το CPLD με τον εξωτερικό κόσμο. Η αρχιτεκτονική του CPLD φαίνεται παρακάτω.

Γενικά, το προγραμματιζόμενο FB μοιάζει με το συστοιχία λογικών πυλών , όπου μπορεί να προγραμματιστεί μια σειρά πυλών AND και οι πύλες OR είναι σταθερές. Όμως, κάθε κατασκευαστής έχει τον τρόπο σκέψης του για να σχεδιάσει το λειτουργικό μπλοκ. Μπορείτε να βρείτε ένα αναφερόμενο o / p λειτουργώντας τα σήματα ανάδρασης που επιτυγχάνονται από τις εξόδους πύλης OR.

Αρχιτεκτονική CPLD

Στον προγραμματισμό CPLD, ο σχεδιασμός κωδικοποιείται για πρώτη φορά σε γλώσσα Verilog ή VHDL μόλις ο κώδικας (προσομοιωθεί και συντεθεί. Κατά τη διάρκεια της σύνθεσης, το μοντέλο CPLD (συσκευή προορισμού) επιλέγεται με το χέρι και δημιουργείται μια λίστα καθαρού χαρτογράφησης με βάση την τεχνολογία. Αυτή η λίστα μπορεί να είναι κοντά -σύνδεση με την αυθεντική αρχιτεκτονική CPLD χρησιμοποιώντας μια διαδικασία θέσης και διαδρομής, που συνήθως επιτυγχάνεται από το λογισμικό τοποθεσίας και διαδρομής του ιδιόκτητου CPLD Company. Στη συνέχεια, ο χειριστής θα κάνει κάποιες διαδικασίες επιβεβαίωσης. Εάν όλα είναι καλά, θα χρησιμοποιήσει το CPLD, αλλιώς θα το αναδιατάξει.

Θέματα αρχιτεκτονικής της CPLD

Κατά την εξέταση μιας σύνθετης προγραμματιζόμενης λογικής συσκευής για χρήση στο σχεδιασμό, υπάρχουν ορισμένα ακόλουθα ζητήματα αρχιτεκτονικής που μπορούν να ληφθούν υπόψη

- Η τεχνολογία προγραμματισμού

- Η ικανότητα μπλοκ λειτουργίας

- Η δυνατότητα I / O

Ορισμένες από τις οικογένειες του CPLD από διαφορετικούς λιανοπωλητές περιλαμβάνουν

- Altera MAX 7000 και MAX 9000 οικογένειες

- Οικογένειες Atmel ATF και ATV

- Lattice isp LSI οικογένεια

- Οικογένεια Lattice (Vantis)

- Οικογένεια Xilinx XC9500

Οικογένειες CPLD

Εφαρμογές του CPLD

Οι εφαρμογές των CPLD περιλαμβάνουν τα ακόλουθα

- Οι σύνθετες προγραμματιζόμενες λογικές συσκευές είναι ιδανικές για εφαρμογές υψηλής απόδοσης και κρίσιμου ελέγχου.

- Το CPLD μπορεί να χρησιμοποιηθεί σε ψηφιακά σχέδια για την εκτέλεση των λειτουργιών του boot loader

- Το CPLD χρησιμοποιείται για τη φόρτωση των δεδομένων διαμόρφωσης ενός πεδίου προγραμματιζόμενης συστοιχίας πυλών από μη πτητική μνήμη.

- Γενικά, αυτά χρησιμοποιούνται σε εφαρμογές μικρού σχεδιασμού, όπως αποκωδικοποίηση διευθύνσεων

- Οι εφαρμογές CPLD χρησιμοποιούνται συχνά σε πολλές εφαρμογές, όπως σε φορητές συσκευές που είναι ευαίσθητες στο κόστος, με μπαταρία λόγω του χαμηλού μεγέθους και της χρήσης χαμηλής ισχύος.

Έτσι, αυτό αφορά την πολύπλοκη προγραμματιζόμενη αρχιτεκτονική συσκευών λογικής και τις εφαρμογές της. Ελπίζουμε να έχετε καλύτερη κατανόηση αυτής της έννοιας. Επιπλέον, τυχόν ερωτήσεις σχετικά με αυτήν την ιδέα ή για την υλοποίηση οποιωνδήποτε ηλεκτρικών και ηλεκτρονικών έργων , δώστε τις πολύτιμες προτάσεις σας σχολιάζοντας την παρακάτω ενότητα σχολίων. Εδώ είναι μια ερώτηση για εσάς, ποια είναι η διαφορά μεταξύ CPLD και FPGA;

Φωτογραφικές μονάδες:

- CPLD wikimedia

- Αρχιτεκτονική του CPLD slidesharecdn