Το κύριο μειονέκτημα του συνδυαστικό κύκλωμα είναι, δεν χρησιμοποιεί καμία μνήμη για να αποθηκεύσει την παρούσα και την προηγούμενη κατάσταση. Ως εκ τούτου, η προηγούμενη κατάσταση εισόδου δεν επηρεάζει την παρούσα κατάσταση του κυκλώματος. Ενώ, το διαδοχικό κύκλωμα έχει μνήμη, οπότε η έξοδος μπορεί να διαφέρει ανάλογα με την είσοδο. Αυτός ο τύπος κυκλωμάτων χρησιμοποιεί προηγούμενη είσοδο, έξοδο, ρολόι και στοιχείο μνήμης. Εδώ τα στοιχεία μνήμης μπορεί να είναι μανδάλωση ή σαγιονάρες. Τα διαδοχικά κυκλώματα έχουν σχεδιαστεί με διάφορες μεθόδους όπως με τη χρήση ROM και flip, PLA, CPLDs (Σύνθετη προγραμματιζόμενη λογική συσκευή) , FPGAs (Field Programmable Gate Array) . Σε αυτό το άρθρο, θα συζητήσουμε μόνο για το πώς να σχεδιάσουμε ένα διαδοχικό κύκλωμα χρησιμοποιώντας PLA.

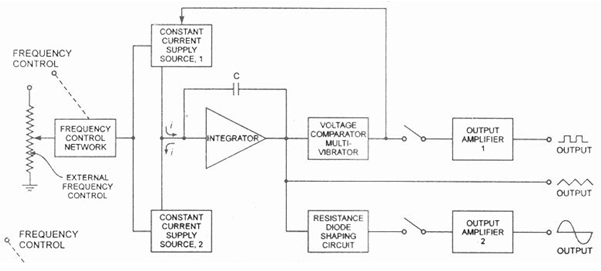

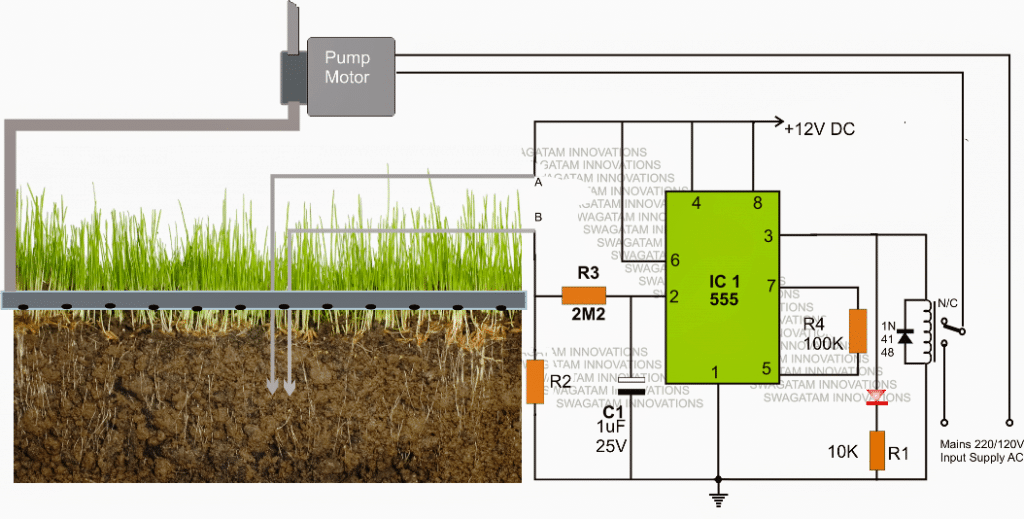

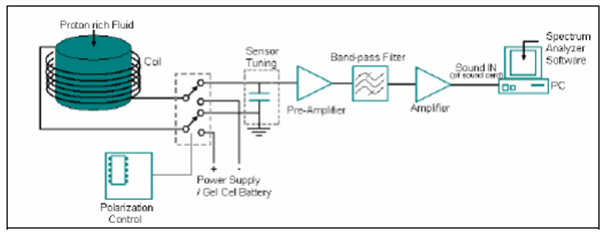

Το μπλοκ διάγραμμα του διαδοχικού κυκλώματος όπως φαίνεται παρακάτω:

Διάγραμμα μπλοκ διαδοχικού κυκλώματος

Σχεδιασμός Sequential Circuit χρησιμοποιώντας PLAs

Διαδοχικά κυκλώματα μπορεί να πραγματοποιηθεί χρησιμοποιώντας PLAs (Programmable Logic Arrays) και flip-flops. Σε αυτό το σχέδιο, η εκχώρηση κατάστασης μπορεί να είναι σημαντική επειδή η χρήση μιας εκχώρησης καλής κατάστασης μπορεί να μειώσει τον απαιτούμενο αριθμό όρων προϊόντος και, ως εκ τούτου, να μειώσει το απαιτούμενο μέγεθος του PLA. Ένας όρος προϊόντος που ορίζεται ως η σύνδεση των κυριολεκτικών λέξεων, όπου κάθε κυριολεκτική είναι είτε μια μεταβλητή είτε η άρνησή της.

Για ας εξετάσουμε το σχεδιασμό έναν μετατροπέα κώδικα. Ο πίνακας κατάστασης που φαίνεται παρακάτω στον πίνακα μπορεί να πραγματοποιηθεί χρησιμοποιώντας ένα PLA και τρία σαγιονάρες όπως φαίνεται παρακάτω σχήμα. Αυτή η διαμόρφωση κυκλώματος είναι πολύ παρόμοια με τη σχεδίαση με βάση το flip-flop ROM, εκτός από το ότι το ROM αντικαθίσταται από το κατάλληλο μέγεθος PLA. Η ανάθεση κατάστασης οδηγεί στον πίνακα αλήθειας που δίνεται παρακάτω. Αυτός ο πίνακας θα μπορούσε να αποθηκευτεί σε ένα PLA με τέσσερις εισόδους, 13 όρους προϊόντος και τέσσερις εξόδους, αλλά αυτό θα προσφέρει μικρότερο μέγεθος σε σύγκριση με το ROM 16 λέξεων.

| X Q1 Q2 Q3 | Με D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 Χ Χ Χ Χ 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 Χ Χ Χ Χ Χ Χ Χ Χ |

Πίνακας: Πίνακας αλήθειας

ΠΑΡΟΝ ΚΑΤΑΣΤΑΣΗ

| ΕΠΟΜΕΝΟ ΚΡΑΤΟΣ X = 0 1 | ΠΑΡΟΝ ΕΞΟΔΟΣ (Z) |

| ΠΡΟΣ ΤΗΝ | ΠΡΟ ΧΡΙΣΤΟΥ | 1 0 |

σι ντο | Δ Ε Και Ε | 1 0 0 1 |

ρε ΕΙΝΑΙ | Η Χ Η Μ | 0 1 1 0 |

Η Μ | Α ΠΡΟΣ ΤΗΝ - | 0 1 1 - |

Πίνακας: Πίνακας κατάστασης

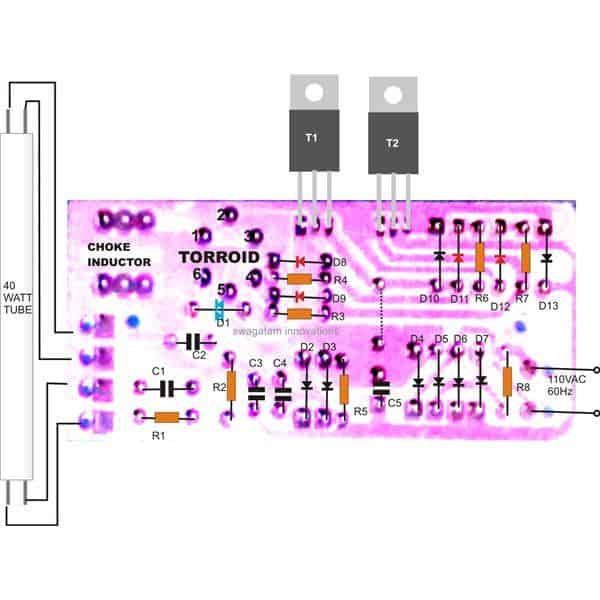

Σχεδιασμός διαδοχικών κυκλωμάτων με χρήση PLA

Εξισώσεις εξόδου εισόδου που προέρχονται από τον χάρτη Karnaugh

Εδώ, καθώς υπάρχουν επτά καταστάσεις, απαιτούνται τρία flip-flop. Έτσι, απαιτείται ένα κύκλωμα PLA με 4 εισόδους και 4 εξόδους. Εάν ληφθεί υπόψη η εκχώρηση κατάστασης του μετατροπέα κώδικα, η προκύπτουσα εξίσωση εξόδου και οι εξισώσεις εισόδου D flip-flop που προέρχονται από το Karnaugh μπορούν να γραφτούν οι ακόλουθες εξισώσεις

D1 = Q1 + = Q2 '

D2 = Q2 + = Q2 '

D3 = Q3 + = Q1 Q2 Q3 = X 'Q1 Q3' = X Q1 'Q2'

Z = X 'Q3' + X Q3

| X Q1 Q2 Q3 | Με D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 έντεκα

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

Ο πίνακας PLA που αντιστοιχεί σε αυτές τις εξισώσεις δίνεται στον παραπάνω πίνακα. Αυτός ο πίνακας μπορεί να πραγματοποιηθεί χρησιμοποιώντας PLA με τέσσερις εισόδους, επτά όρους προϊόντος και τέσσερις εξόδους. Για να επαληθεύσετε αρχικά τη λειτουργία του παραπάνω σχεδιασμού, υποθέστε ότι X = 0 και Q1Q2Q3 = 000. Αυτό επιλέγει σειρές - - 0- και 0 - - -0 στον πίνακα, οπότε Z = 0 και D1D2D3 = 100. Μετά το ενεργό άκρο ρολογιού, Q1Q2Q3 = 100. Εάν η επόμενη είσοδος είναι X = 1, τότε επιλέγονται οι σειρές - - 0 - και - 1- -, οπότε Z = 0 και D1D2D3 = 110. Μετά το ενεργό άκρο ρολογιού, Q1Q2Q3 = 110.

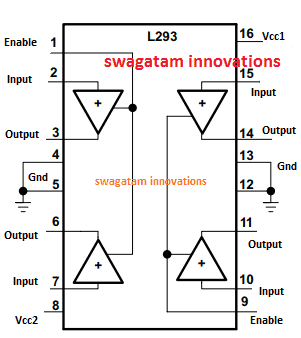

Προγραμματιζόμενη λογική σειρά (PLA)

Το Programmable Logic Array είναι μια προγραμματιζόμενη λογική συσκευή. Χρησιμοποιείται γενικά για την εφαρμογή συνδυαστικών κυκλωμάτων λογικής. Το PLA έχει ένα σύνολο προγραμματιζόμενων επιπέδων AND (συστοιχία AND), που συνδέονται με ένα σύνολο προγραμματιζόμενων επιπέδων OR (συστοιχία OR), το οποίο μπορεί στη συνέχεια να συμπληρωθεί προσωρινά για να παραχθεί μια έξοδος. Αυτή η διάταξη επιτρέπει τη σύνθεση μεγάλου αριθμού λογικών συναρτήσεων στο άθροισμα προϊόντων (SOP) κανονικές μορφές. Ένα απλό μπλοκ διάγραμμα ενός PLA δίνεται παρακάτω.

Διάγραμμα μπλοκ ενός PLA

Η κύρια διαφορά μεταξύ PLA και PAL (λογική προγραμματιζόμενης συστοιχίας) είναι,

PLA: Και τα δύο ΚΑΙ αεροπλάνο και αεροπλάνο είναι προγραμματιζόμενα.

PAL: Μόνο το επίπεδο AND είναι προγραμματιζόμενο, ενώ το επίπεδο OR είναι σταθερό.

Για την καλύτερη κατανόηση του PLA, εδώ εξετάζουμε το παρακάτω παράδειγμα.

Ας προσπαθήσουμε να εφαρμόσουμε αυτές τις συναρτήσεις f1 και f2 δίνονται ως

Οι είσοδοι x1, x2, x3 και τα αντίστοιχα συμπληρωμένα σήματά τους δίδονται στο προγραμματιζόμενο επίπεδο AND, εκεί θα λάβουμε εξόδους AND επίπεδο ως P1, P2, P3 καλούμενα minterms. Στη συνέχεια, αυτά τα σήματα δίδονται στο προγραμματιζόμενο επίπεδο OR για την παραγωγή της απαιτούμενης λειτουργίας εξόδου f1 και f2 (άθροισμα προϊόντων). Το παρακάτω σχήμα περιγράφει την εφαρμογή σε επίπεδο πύλης του PLA για δεδομένη λειτουργικότητα.

Εφαρμογή του PLA

Αυτό αφορά το σχεδιασμό διαδοχικών κυκλωμάτων με χρήση PLA. Θεωρούμε ότι οι πληροφορίες που δίνονται σε αυτό το άρθρο είναι χρήσιμες για την καλύτερη κατανόηση αυτής της έννοιας. Επιπλέον, τυχόν απορίες σχετικά με αυτό το άρθρο ή οποιαδήποτε βοήθεια στο υλοποίηση ηλεκτρικών και ηλεκτρονικών έργων , μπορείτε να επικοινωνήσετε μαζί μας σχολιάζοντας την παρακάτω ενότητα σχολίων. Εδώ είναι μια ερώτηση για εσάς, Τι σημαίνει ένα διαδοχικό κύκλωμα;