ο τρανζίστορ εφέ πεδίου (FET) είναι μια ηλεκτρονική συσκευή στην οποία ηλεκτρικό πεδίο χρησιμοποιείται για τη ρύθμιση της ροής του ρεύματος. Για την εφαρμογή αυτού εφαρμόζεται μια πιθανή διαφορά μεταξύ των ακροδεκτών πύλης και πηγής της συσκευής, η οποία μεταβάλλει την αγωγιμότητα μεταξύ των ακροδεκτών αποστράγγισης και πηγής προκαλώντας ροή ελεγχόμενου ρεύματος σε αυτούς τους ακροδέκτες.

Οι FET καλούνται μονοπολικά τρανζίστορ επειδή έχουν σχεδιαστεί για να λειτουργούν ως συσκευές τύπου ενός φορέα. Θα βρείτε διαφορετικούς τύπους τρανζίστορ εφέ πεδίου διαθέσιμους.

Σύμβολο

Τα γραφικά σύμβολα για τα κανάλια n-καναλιών και p-καναλιών μπορούν να απεικονιστούν στα ακόλουθα σχήματα.

Μπορείτε να παρατηρήσετε ξεκάθαρα ότι τα σημάδια βέλους που δείχνουν προς τα μέσα για τη συσκευή κανάλι n για να υποδείξουν την κατεύθυνση στην οποία Iσολ(πύλη ρεύματος) υποτίθεται ότι ρέει όταν η διασταύρωση p-n ήταν προς τα εμπρός.

Σε περίπτωση συσκευής καναλιού p οι συνθήκες είναι ίδιες εκτός από τη διαφορά στην κατεύθυνση του συμβόλου βέλους.

Διαφορά μεταξύ FET και BJT

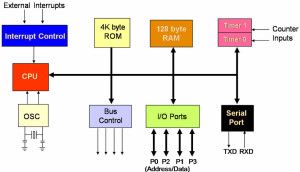

Το τρανζίστορ πεδίου εφέ (FET) είναι μια συσκευή τριών τερματικών που έχει σχεδιαστεί για ένα ευρύ φάσμα εφαρμογών κυκλώματος που συμπληρώνουν, σε μεγάλο βαθμό, αυτές του τρανζίστορ BJT.

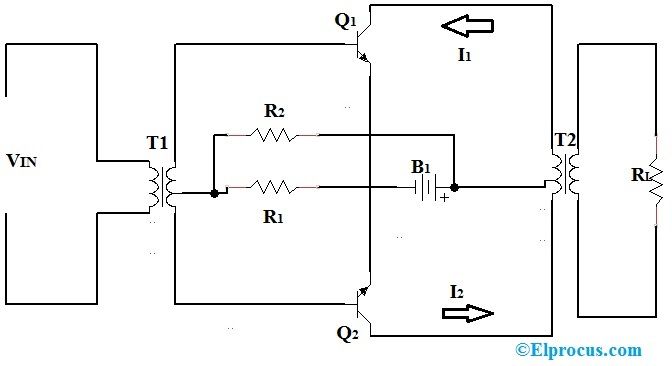

Ενώ θα βρείτε σημαντικές διαφορές μεταξύ BJT και JFET, υπάρχουν στην πραγματικότητα αρκετά χαρακτηριστικά που ταιριάζουν στις ακόλουθες συζητήσεις. Η κύρια διάκριση μεταξύ αυτών των συσκευών είναι το BJT είναι μια ελεγχόμενη από το ρεύμα συσκευή όπως απεικονίζεται στο Σχ. 5.1α, ενώ το τρανζίστορ JFET είναι μια ελεγχόμενη τάση συσκευή όπως υποδεικνύεται στο Σχ. 5.1b.

Με απλά λόγια, το τρέχον Iντοστο Σχ. 5.1α είναι μια άμεση συνάρτηση του επιπέδου Iσι. Για το FET το ρεύμα I είναι συνάρτηση της τάσης VGSδίνεται στο κύκλωμα εισόδου όπως φαίνεται στο Σχ. 5.1b.

Και στις δύο περιπτώσεις το ρεύμα του κυκλώματος εξόδου θα διέπεται από μια παράμετρο του κυκλώματος εισόδου. Σε μια κατάσταση ένα τρέχον επίπεδο και στην άλλη μια εφαρμοζόμενη τάση.

Ακριβώς όπως npn και pnp για διπολικά τρανζίστορ, θα βρείτε τρανζίστορ πεδίου εφέ-καναλιού και p-καναλιού. Όμως, πρέπει να θυμάστε ότι το τρανζίστορ BJT είναι μια διπολική συσκευή, το πρόθεμα που δείχνει ότι το επίπεδο αγωγιμότητας είναι συνάρτηση δύο φορέων φόρτισης, ηλεκτρονίων και οπών.

Το FET από την άλλη είναι ένα μονοπολική συσκευή που εξαρτάται αποκλειστικά από την αγωγιμότητα ηλεκτρονίων (κανάλι n) ή οπής (κανάλι p).

Η φράση «πεδίο-εφέ» μπορεί να εξηγηθεί ως εξής: όλοι μας γνωρίζουμε τη δύναμη ενός μόνιμου μαγνήτη να προσελκύει μεταλλικά νήματα προς τον μαγνήτη χωρίς φυσική επαφή. Με παρόμοιο τρόπο μέσα στο FET δημιουργείται ένα ηλεκτρικό πεδίο από τα υπάρχοντα φορτία που επηρεάζουν τη διαδρομή αγωγής του κυκλώματος εξόδου χωρίς να υπάρχει άμεση επαφή μεταξύ των ελεγχόμενων και ελεγχόμενων ποσοτήτων. Μάλλον ένα από τα πιο σημαντικά χαρακτηριστικά του FET είναι η υψηλή αντίσταση εισόδου.

Το εύρος από 1 έως εκατοντάδες megohms ξεπερνά σημαντικά τα κανονικά εύρη αντίστασης εισόδου των διαμορφώσεων BJT, ένα εξαιρετικά σημαντικό χαρακτηριστικό κατά την ανάπτυξη γραμμικών μοντέλων ενισχυτή ac.

Ωστόσο, το BJT φέρει μεγαλύτερη ευαισθησία στις μεταβολές του σήματος εισόδου. Δηλαδή, η αλλαγή στο ρεύμα εξόδου είναι συνήθως πολύ μεγαλύτερη για τα BJT από τα FET για το ίδιο ποσό αλλαγής στις τάσεις εισόδου τους.

Εξαιτίας αυτού, τα τυπικά κέρδη τάσης εναλλασσόμενου ρεύματος για ενισχυτές BJT μπορεί να είναι πολύ υψηλότερα σε σύγκριση με τα FET.

Σε γενικές γραμμές, τα FET είναι πολύ πιο θερμικά ανθεκτικά από τα BJT και συχνά έχουν μικρότερο μέγεθος σε σύγκριση με τα BJT, τα οποία τα καθιστούν ειδικά κατάλληλα για ενσωμάτωση ως ολοκληρωμένο κύκλωμα (IΝΤΟ)μάρκες.

Τα δομικά χαρακτηριστικά ορισμένων FET, από την άλλη πλευρά, μπορούν να τους επιτρέψουν να είναι πολύ ευαίσθητοι στις φυσικές επαφές από τους BJTs.

Περισσότερη σχέση BJT / JFET

- Για BJT VΕΙΝΑΙ= 0,7 V είναι ο σημαντικός παράγοντας για την έναρξη μιας ανάλυσης της διαμόρφωσής του.

- Ομοίως, η παράμετρος Ισολ= 0 A είναι συνήθως το πρώτο πράγμα που εξετάζεται για την ανάλυση ενός κυκλώματος JFET.

- Για τη διαμόρφωση BJT, Iσιείναι συχνά ο πρώτος παράγοντας που καθίσταται απαραίτητος για να καθοριστεί.

- Ομοίως, για το JFET, είναι συνήθως το VGS.

Σε αυτό το άρθρο θα επικεντρωθούμε σε JFET ή τρανζίστορ εφέ πεδίου διασταύρωσης, στο επόμενο άρθρο θα συζητήσουμε για το τρανζίστορ πεδίου-ημιαγωγού μετάλλου-οξειδίου ή το MOS-FET.

ΚΑΤΑΣΚΕΥΗ ΚΑΙ ΧΑΡΑΚΤΗΡΙΣΤΙΚΑ ΤΟΥ JFET

Όπως μάθαμε το ακουστικό ένα JFET έχει 3 δυνητικούς πελάτες. Ένας από αυτούς ελέγχει την τρέχουσα ροή μεταξύ των άλλων δύο.

Ακριβώς όπως τα BJT, και στα JFET, η συσκευή κανάλι n χρησιμοποιείται πιο εμφανώς από τα αντίστοιχα κανάλια p, καθώς οι συσκευές n τείνουν να είναι πιο αποτελεσματικές και φιλικές προς τον χρήστη σε σύγκριση με τη συσκευή p.

Στο παρακάτω σχήμα μπορούμε να δούμε τη βασική δομή ή την κατασκευή ενός καναλιού JFET. Μπορούμε να δούμε ότι η σύνθεση τύπου-n σχηματίζει το κύριο κανάλι στα επίπεδα του τύπου p.

Το άνω μέρος του καναλιού τύπου n συνδέεται μέσω μιας επαφής Ohmic με ένα τερματικό που ονομάζεται drain (D), ενώ το κάτω τμήμα του ίδιου καναλιού συνδέεται επίσης μέσω μιας επαφής Ohmic με ένα άλλο τερματικό που ονομάζεται πηγή (S).

Το ζευγάρι των υλικών τύπου p συνδέονται μαζί με τον ακροδέκτη που αναφέρεται ως πύλη (G). Βασικά διαπιστώνουμε ότι οι ακροδέκτες αποστράγγισης και πηγής συνδέονται στα άκρα του καναλιού τύπου-n. Το τερματικό πύλης συνδέεται με ένα ζευγάρι υλικού καναλιού p.

Όταν δεν υπάρχει τάση σε ένα jfet, οι δύο συνδέσεις του p-n είναι χωρίς συνθήκες πόλωσης. Σε αυτήν την περίπτωση υπάρχει μια περιοχή εξάντλησης σε κάθε διασταύρωση όπως φαίνεται στο παραπάνω σχήμα, η οποία μοιάζει αρκετά με μια περιοχή διόδων p-n χωρίς πόλωση.

Αναλογία νερού

Οι λειτουργίες λειτουργίας και ελέγχου ενός JFET μπορούν να γίνουν κατανοητές μέσω της ακόλουθης αναλογίας νερού.

Εδώ, η πίεση του νερού μπορεί να συγκριθεί με το εφαρμοζόμενο μέγεθος τάσης από την αποστράγγιση προς την πηγή.

Η ροή του νερού μπορεί να συγκριθεί με τη ροή των ηλεκτρονίων. Το στόμιο της βρύσης μιμείται τον ακροδέκτη πηγής του JFET, ενώ το άνω μέρος της βρύσης όπου το νερό πιέζεται απεικονίζει την αποστράγγιση του JFET.

Το κουμπί επιλογής λειτουργεί όπως η Πύλη του JFET. Με τη βοήθεια ενός δυναμικού εισόδου ελέγχει τη ροή ηλεκτρονίων (φόρτιση) από την αποστράγγιση στην πηγή, ακριβώς όπως το κουμπί βρύσης ελέγχει τη ροή του νερού στο άνοιγμα του στόματος.

Από τη δομή JFET μπορούμε να δούμε ότι οι ακροδέκτες αποστράγγισης και πηγής βρίσκονται στα αντίθετα άκρα του καναλιού n και καθώς ο όρος βασίζεται στη ροή ηλεκτρονίων μπορούμε να γράψουμε:

ΒGS= 0 V, VDSΚάποια θετική αξία

Στο Σχ. 5.4 μπορούμε να δούμε μια θετική τάση VDSεφαρμόζεται σε ολόκληρο το κανάλι n. Το τερματικό πύλης συνδέεται απευθείας με την πηγή για να δημιουργήσει μια συνθήκη VGS= 0V. Αυτό επιτρέπει στην πύλη και τους ακροδέκτες της πηγής να έχουν το ίδιο δυναμικό και οδηγεί σε μια περιοχή εξάντλησης κατώτερου άκρου κάθε υλικού p, ακριβώς όπως βλέπουμε στο πρώτο διάγραμμα παραπάνω με συνθήκη χωρίς προκατάληψη.

Μόλις μια τάση VΔΔ(= VDSεφαρμόζεται, τα ηλεκτρόνια τραβιούνται προς τον ακροδέκτη αποστράγγισης, δημιουργώντας τη συμβατική ροή του ρεύματος ID, όπως φαίνεται στο Σχ. 5.4.

Η κατεύθυνση της ροής του φορτίου αποκαλύπτει ότι το ρεύμα αποστράγγισης και πηγής είναι ίσο σε μέγεθος (Iρε= Εγώμικρό). Σύμφωνα με τις συνθήκες που απεικονίζονται στο Σχ. 5.4, η ροή του φορτίου φαίνεται αρκετά απεριόριστη και επηρεάζεται μόνο από την αντίσταση του κανάλι n μεταξύ αποστράγγισης και πηγής.

Μπορεί να παρατηρήσετε ότι η περιοχή εξάντλησης είναι μεγαλύτερη γύρω από το επάνω τμήμα και των δύο υλικών τύπου p. Αυτή η διαφορά στο μέγεθος της περιοχής εξηγείται ιδανικά μέσω του σχήματος 5.5. Ας φανταστούμε ότι έχει μια ομοιόμορφη αντίσταση στο κανάλι n, αυτό θα μπορούσε να χωριστεί στα τμήματα που αναφέρονται στο Σχ. 5.5.

Το τρέχον εγώρεμπορεί να δημιουργήσει τα εύρη τάσης μέσω του καναλιού όπως επισημαίνεται στο ίδιο σχήμα. Ως αποτέλεσμα, η άνω περιοχή του υλικού τύπου ρ πρόκειται να αντιστραφεί με αντίσταση κατά επίπεδο περίπου 1,5 V, με την κάτω περιοχή να είναι απλώς αντίστροφη μεροληψία κατά 0,5 V.

Το σημείο που η διασταύρωση p-n είναι αντίστροφη προκατειλημμένη σε ολόκληρο το κανάλι δημιουργεί ρεύμα πύλης με μηδενικές αμπέρ όπως φαίνεται στο ίδιο σχήμα. Αυτό το χαρακτηριστικό που οδηγεί σε Iσολ= 0 A είναι ένα σημαντικό χαρακτηριστικό του JFET.

Ως VDSτο δυναμικό αυξάνεται από 0 σε μερικά βολτ, το ρεύμα αυξάνεται σύμφωνα με τον νόμο του Ohm και την πλοκή του Iρεγραμμή 5DSμπορεί να φαίνεται όπως αποδεικνύεται στο Σχ. 5.6.

Η συγκριτική ευθυγράμμιση της γραφικής παράστασης δείχνει ότι για τις περιοχές χαμηλής αξίας του VDS, η αντίσταση είναι βασικά ομοιόμορφη. Ως VDSανεβαίνει και πλησιάζει ένα επίπεδο γνωστό ως VP στο Σχ. 5.6, οι περιοχές εξάντλησης διευρύνονται όπως δίδεται στο Σχ. 5.4.

Αυτό έχει ως αποτέλεσμα την εμφανή μείωση του πλάτους του καναλιού. Η μειωμένη διαδρομή αγωγιμότητας οδηγεί στην αύξηση της αντίστασης που προκαλεί την καμπύλη του Σχ. 5.6.

Όσο πιο οριζόντια γίνεται η καμπύλη, τόσο υψηλότερη είναι η αντίσταση, υποδηλώνοντας ότι η αντίσταση πλησιάζει στα 'άπειρα' ωμ στην οριζόντια περιοχή. Όταν VDSαυξάνεται σε βαθμό που φαίνεται ότι οι δύο περιοχές εξάντλησης ενδέχεται να «έρχονται σε επαφή» όπως φαίνεται στο Σχ. 5.7, δημιουργεί μια κατάσταση γνωστή ως τσίμπημα.

Το ποσό κατά το οποίο VDSαναπτύσσει αυτήν την κατάσταση ονομάζεται τσίμπημα τάση και συμβολίζεται με VΠόπως παρουσιάζεται στο Σχ. 5.6. Σε γενικές γραμμές, η λέξη pinch-off είναι παραπλανητική επειδή υπονοεί το τρέχον Iρεείναι «τρυπημένο» και πέφτει στο 0 A. Όπως αποδεικνύεται στο Σχ. 5.6, αυτό φαίνεται ελάχιστα εμφανές σε αυτήν την περίπτωση. Εγώρεδιατηρεί ένα επίπεδο κορεσμού που χαρακτηρίζεται ως IDSSστο Σχ. 5.6.

Η αλήθεια είναι ότι ένα πολύ μικρό κανάλι συνεχίζει να υπάρχει, με ρεύμα σημαντικά υψηλής συγκέντρωσης.

Το σημείο στο οποίο δεν αναγνωρίζεται το αναγνωριστικό τσίμπημα και διατηρεί το επίπεδο κορεσμού όπως υποδεικνύεται στο Σχ. 5.6 επιβεβαιώνεται με την ακόλουθη απόδειξη:

Δεδομένου ότι δεν υπάρχει ρεύμα αποστράγγισης, εξαλείφεται η πιθανότητα διαφορετικών δυνατοτήτων μέσω του υλικού καναλιού για τον προσδιορισμό των μεταβαλλόμενων ποσοτήτων αντίστροφης μεροληψίας κατά μήκος της σύνδεσης p-n. Το τελικό αποτέλεσμα είναι η απώλεια της κατανομής της περιοχής εξάντλησης που πυροδότησε τσίμπημα να ξεκινήσει με.

Καθώς αυξάνουμε το VDSπάνω από το VΠ, η περιοχή στενής επαφής όπου οι δύο περιοχές εξάντλησης θα συναντηθούν μεταξύ τους με αύξηση μήκους κατά μήκος του καναλιού. Ωστόσο, το επίπεδο ταυτότητας εξακολουθεί να είναι ουσιαστικά αμετάβλητο.

Έτσι, η στιγμή VDSείναι υψηλότερο από το VΠ, το JFET αποκτά τα χαρακτηριστικά της τρέχουσας πηγής.

Όπως αποδεικνύεται στο Σχήμα 5.8 το ρεύμα σε JFET καθορίζεται στο Iρε= ΕγώDSS, αλλά τάση VDSυψηλότερο από το VP καθορίζεται από το συνδεδεμένο φορτίο.

Η επιλογή του συμβολισμού IDSS βασίζεται στο γεγονός ότι είναι το ρεύμα Drain to Source που έχει βραχυκυκλωμένο σύνδεσμο σε όλη την πύλη προς την πηγή.

Η περαιτέρω έρευνα μας δίνει την ακόλουθη αξιολόγηση:

ΕγώDSSείναι το υψηλότερο ρεύμα αποστράγγισης για ένα JFET και καθορίζεται από τις συνθήκες VGS= 0 V και VDS> | VP |.

Παρατηρήστε ότι στο Σχ. 5.6 VGSείναι 0V για την πλήρη έκταση της καμπύλης. Στις ακόλουθες ενότητες θα μάθουμε πώς επηρεάζονται τα χαρακτηριστικά του Σχ. 5.6 ως το επίπεδο του VGSποικίλλει.

ΒGS <0V

Η τάση που εφαρμόζεται σε όλη την πύλη και την πηγή δηλώνεται ως το VGS, το οποίο είναι υπεύθυνο για τον έλεγχο των λειτουργιών JFET.

Αν πάρουμε το παράδειγμα ενός BJT, όπως και οι καμπύλες του Iντοεναντίον VΑΥΤΟκαθορίζονται για διάφορα επίπεδα Iσι, ομοίως οι καμπύλες του Iρεεναντίον VDSγια διάφορα επίπεδα VGSμπορεί να δημιουργηθεί για ένα αντίστοιχο JFET.

Γι 'αυτό το τερματικό πύλης ρυθμίζεται σε συνεχές χαμηλότερο δυναμικό κάτω από το επίπεδο του δυναμικού πηγής.

Αναφερόμενοι στο Σχ.5.9 παρακάτω, a -1V εφαρμόζεται στους ακροδέκτες πύλης / πηγής για μειωμένο VDSεπίπεδο.

Ο στόχος της αρνητικής δυνητικής προκατάληψης VGSείναι η ανάπτυξη περιοχών εξάντλησης που μοιάζουν με την κατάσταση του VGS= 0, αλλά σε σημαντικά μειωμένο VDS.

Αυτό αναγκάζει την πύλη να επιτύχει ένα σημείο κορεσμού με χαμηλότερα επίπεδα VDSόπως υποδεικνύεται στο Σχ. 5.10 (VGS= -1V).

Το αντίστοιχο επίπεδο κορεσμού για Iρεμπορεί να βρεθεί ότι μειώνεται και στην πραγματικότητα συνεχίζει να μειώνεται ως VGSγίνεται πιο αρνητικό.

Μπορείτε να δείτε ξεκάθαρα στο Σχ. 5.10 πώς η τάση αποσυμπίεσης συνεχίζει να πέφτει με παραβολικό σχήμα ως VGSγίνεται όλο και πιο αρνητικό.

Τέλος, όταν VGS= -VΠ, γίνεται αρκετά αρνητικό για να καθορίσει ένα επίπεδο κορεσμού που είναι τελικά 0 mA. Σε αυτό το επίπεδο, το JFET είναι εντελώς «απενεργοποιημένο».

Το επίπεδο του VGSπου προκαλεί εγώρεγια να φτάσετε 0 mA χαρακτηρίζεται από VGS= VΠ, όπου VΠείναι μια αρνητική τάση για συσκευές καναλιού και θετική τάση για JFETs καναλιού p.

Συνήθως, ενδέχεται να εμφανίζονται τα περισσότερα φύλλα δεδομένων JFET τσίμπημα η τάση καθορίζεται ως VGS (απενεργοποιημένο)αντί για VΠ.

Η περιοχή στη δεξιά πλευρά του τόπου αποκοπής στο παραπάνω σχήμα είναι η θέση που χρησιμοποιείται συμβατικά σε γραμμικούς ενισχυτές για την επίτευξη σήματος χωρίς παραμόρφωση. Αυτή η περιοχή ονομάζεται γενικά περιοχή σταθερού ρεύματος, κορεσμού ή γραμμικής ενίσχυσης.

Αντίσταση ελεγχόμενη από τάση

Η περιοχή που βρίσκεται στην αριστερή πλευρά του σημείου αποκοπής στο ίδιο σχήμα, ονομάζεται ωμική περιοχή ή περιοχή ελεγχόμενης τάσης.

Σε αυτήν την περιοχή η συσκευή μπορεί στην πραγματικότητα να λειτουργεί ως μεταβλητή αντίσταση (για παράδειγμα σε εφαρμογή αυτόματου ελέγχου κέρδους), με την αντίστασή της να ελέγχεται μέσω του δυναμικού πύλης / πηγής που εφαρμόζεται.

Μπορείτε να δείτε ότι η κλίση καθεμιάς από τις καμπύλες που δείχνει επίσης την αντίσταση αποστράγγισης / πηγής του JFET για VDS

Καθώς αυξάνουμε το VGS με αρνητικό δυναμικό, η κλίση κάθε καμπύλης γίνεται όλο και πιο οριζόντια, παρουσιάζοντας αναλογικά αυξανόμενα επίπεδα αντίστασης.

Μπορούμε να πάρουμε μια καλή αρχική προσέγγιση στο επίπεδο της αντίστασης σε σχέση με την τάση VGS, μέσω της ακόλουθης εξίσωσης.

p-Channel JFET λειτουργεί

Η εσωτερική διάταξη και κατασκευή ενός καναλιού p JFET είναι ακριβώς όμοια με το αντίστοιχο κανάλι n, εκτός από το ότι οι περιοχές υλικών τύπου p- και n αντιστρέφονται, όπως φαίνεται παρακάτω:

Οι κατευθύνσεις της ροής ρεύματος μπορούν επίσης να θεωρηθούν αντιστρεπτές, μαζί με τις πραγματικές πολικότητες της τάσης VGS και VDS. Στην περίπτωση ενός καναλιού p JFET, το κανάλι θα περιοριστεί ως απάντηση στην αύξηση του θετικού δυναμικού κατά μήκος της πύλης / πηγής.

Η σημειογραφία με διπλή συνδρομή για το VDSθα προκαλέσει αρνητική τάση για VDS, όπως φαίνεται στα χαρακτηριστικά του Σχ.5.12. Εδώ, μπορείτε να βρείτεDSSστα 6 mA, ενώ η τάση απόσβεσης στο VGS= + 6V.

Μην μπερδεύεστε λόγω της παρουσίας σας μείον το σύμβολο για το VDS. Απλώς υποδεικνύει ότι η πηγή έχει υψηλότερο δυναμικό από την αποχέτευση.

Μπορείτε να δείτε ότι οι καμπύλες για υψηλό VDSΤα επίπεδα αυξάνονται απότομα σε τιμές που φαίνονται απεριόριστες. Η υποδεικνυόμενη άνοδος που είναι κάθετα συμβολίζει μια κατάσταση βλάβης, που σημαίνει ότι το ρεύμα μέσω της συσκευής καναλιού ελέγχεται πλήρως από το εξωτερικό κύκλωμα σε αυτό το χρονικό σημείο.

Αν και αυτό δεν είναι εμφανές στο Σχ. 5.10 για τη συσκευή καναλιού, μπορεί να είναι πιθανότητα υπό αρκετά υψηλή τάση.

Αυτή η περιοχή μπορεί να εξαλειφθεί εάν το VDS (μέγ.)σημειώνεται από το φύλλο δεδομένων της συσκευής και η συσκευή έχει διαμορφωθεί έτσι ώστε η πραγματική VDSη τιμή είναι χαμηλότερη από αυτήν την σημειωμένη τιμή για οποιοδήποτε VGS.

Προηγούμενο: Εξερευνήθηκαν 5 καλύτερα κυκλώματα ενισχυτή 40 Watt Επόμενο: Φύλλο δεδομένων 2N3055, Pinout, Κυκλώματα εφαρμογής