Ο όρος VLSI σημαίνει «Τεχνολογία Ενσωμάτωσης Πολύ Μεγάλης Κλίμακας» που περιλαμβάνει το σχεδιασμό ολοκληρωμένων κυκλωμάτων (IC) συνδυάζοντας χιλιάδες τρανζίστορ λογικά σε ένα μόνο chip από διαφορετικά κυκλώματα λογικής . Αυτά τα IC μειώνουν τελικά τον καταλαμβανόμενο χώρο κυκλώματος σε σύγκριση με τα κυκλώματα με συμβατικά IC. Η υπολογιστική ισχύς και η χρήση χώρου είναι οι κύριες προκλήσεις του σχεδιασμού VLSI. Η υλοποίηση έργων VLSI ανοίγει μια προκλητική και φωτεινή καριέρα τόσο για τους μαθητές όσο και για τους ερευνητές. Μερικές από τις νέες τάσεις του VLSI είναι Προγραμματιζόμενη σειρά πινάκων πεδίου εφαρμογές (FPGA), ASIC σχέδια και SOC. Παρακάτω παρατίθεται μια λίστα με ορισμένα από τα έργα VLSI για εκείνους τους μαθητές που αναζητούν σοβαρά έργα σε αυτόν τον τομέα. Αυτό το άρθρο περιγράφει μια επισκόπηση των έργων VLSI που βασίζονται σε FPGA, Xilinx, IEEE, Mini, Matlab κ.λπ. παρατίθενται παρακάτω. Αυτά τα έργα είναι πολύ χρήσιμα για φοιτητές μηχανικής, φοιτητές M.tech.

Έργα VLSI για φοιτητές μηχανικής

Τα έργα VLSI με περιλήψεις για φοιτητές ηλεκτρονικής μηχανικής συζητούνται παρακάτω.

Έργα VLSI

1). Μετασχηματισμός διακριτών Wavelet με 3D Lifting

Αυτό το έργο βοηθά στην παροχή πολύ ακριβών εικόνων χρησιμοποιώντας την κωδικοποίηση μιας εικόνας χωρίς να χάσετε τα δεδομένα της. Για να επιτευχθεί αυτό, αυτή η διαδικασία εφαρμόζει ένα ανυψωτικό φίλτρο ανάλογα με τον μετασχηματισμό της αρχιτεκτονικής 3D διακριτού κύματος VLSI.

2). Σχεδιασμός πολλαπλασιαστή SFQ με 4-bit με αποτελεσματικό μέσω Υψηλής ταχύτητας υλικού

Αυτό το έργο χρησιμοποιείται κυρίως για την εφαρμογή ενός τροποποιημένου κωδικοποιητή θαλάμου (MBE) με 4-bit SFQ πολλαπλασιαστής . Αυτός ο πολλαπλασιαστής παρέχει καλή απόδοση σε σύγκριση με τον συμβατικό κωδικοποιητή θαλάμου. Αυτό το έργο χρησιμοποιείται κυρίως στις εφαρμογές κρίσιμης καθυστέρησης.

3). Επεξεργαστής κρυπτογραφίας που χρησιμοποιείται σε έξυπνες κάρτες με αποτελεσματική περιοχή

Αυτό το έργο χρησιμοποιείται για την εφαρμογή τριών αλγορίθμων κρυπτογραφίας που υποστηρίζονται τόσο από ιδιωτικά όσο και από δημόσια κλειδιά που χρησιμοποιούνται στο έξυπνη κάρτα εφαρμογές για την παροχή εξαιρετικά ασφαλούς επαλήθευσης και δεδομένων χρήστη επικοινωνία .

4). Πολλαπλασιαστής υψηλής ταχύτητας ή χαμηλής ισχύος με μέθοδο ψευδούς καταστολής ισχύος

Αυτό το προτεινόμενο σύστημα φιλτράρει τα άχρηστα ψευδή σήματα αριθμητικών μονάδων για την αποφυγή περιττής μετάδοσης δεδομένων που δεν επηρεάζει τα τελευταία αποτελέσματα υπολογιστών. Αυτό το σύστημα χρησιμοποιεί μια μέθοδο SPST για πολλαπλασιαστές για την επίτευξη μετάδοσης δεδομένων χαμηλής ισχύος και υψηλής ταχύτητας.

5). Συμπίεση και αποσυμπίεση αλγόριθμου δεδομένων χωρίς απώλειες

Αυτό το έργο υλοποιείται κυρίως για αρχιτεκτονική υλικού 2 σταδίων ανάλογα με τη λειτουργία αλγορίθμου PDLZW (Parallel Dictionary LZW), καθώς και τον αλγόριθμο τύπου Adaptive Huffman, ο οποίος χρησιμοποιείται και για τις εφαρμογές συμπίεσης χωρίς απώλεια δεδομένων και αποσυμπίεσης χωρίς απώλειες.

6). Η αρχιτεκτονική του Turbo Decoder με χαμηλή πολυπλοκότητα για ενεργειακά αποδοτικά WSN

Το προτεινόμενο σύστημα χρησιμοποιείται για τη μείωση της συνολικής κατανάλωσης ενέργειας σε όλη τη μετάδοση δεδομένων των WSNs μέσω του αλγορίθμου αποσύνθεσης του LUT-Log-BCJR σε βασικές λειτουργίες ACS (Προσθήκη σύγκρισης επιλογής).

7). VLSI Architecture για την απομάκρυνση του παλμού του θορύβου μιας εικόνας με αποτελεσματικά

Αυτό το προτεινόμενο σύστημα χρησιμοποιείται κυρίως για να βελτιώσει οπτικά την ποιότητα της εικόνας για να αποφευχθούν οι πιθανότητες να καταστραφούν με παλμικό θόρυβο για την εφαρμογή μιας αποτελεσματικής αρχιτεκτονικής VLSI με τη βοήθεια ενός φίλτρου διατήρησης άκρων.

8). Η αρχιτεκτονική ενός επεξεργαστή στη μνήμη που χρησιμοποιείται για τη συμπίεση των πολυμέσων

Αυτό το προτεινόμενο σύστημα παρέχει αρχιτεκτονική χαμηλής πολυπλοκότητας για ένα επεξεργαστής στη μνήμη για την υποστήριξη εφαρμογών πολυμέσων, δηλαδή συμπίεση εικόνας, βίντεο μέσω εφαρμογής τεράστιων μονών οδηγιών, πολλαπλών εννοιών δεδομένων και λέξεων εντολών.

9). Τεχνική συγχρονισμού συγχρονισμού με ρυθμό συμβόλου για ασύρματα συστήματα OFDM με χαμηλή ισχύ

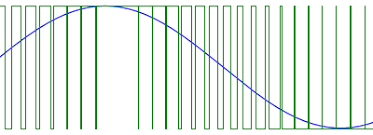

Αυτό το προτεινόμενο σύστημα χρησιμοποιείται κυρίως για τη βελτίωση της δράσης του ασύρματου OFDM (Orthogonal Frequency Division Πολυπλεξία ) σύστημα μέσω της μείωσης της ισχύος ολόκληρης της ζώνης βάσης με τη βοήθεια ενός ρολογιού γεννήτρια με ρυθμιστή φάσης & δυναμικό χρονοδιακόπτη.

10). Υλοποίηση με πολλαπλασιαστή χαμηλής ισχύος και υψηλής ταχύτητας με SPST Adder & Verilog

Αυτό το έργο χρησιμοποιείται για το σχεδιασμό MAC χαμηλής ισχύος & υψηλής ταχύτητας (πολλαπλασιαστής και συσσωρευτής) μέσω αποδοχής της μεθόδου ψευδούς καταστολής ισχύος σε MBE (τροποποιημένος κωδικοποιητής θαλάμου). Με τη χρήση αυτού του σχεδιασμού, μπορεί να αποφευχθεί η απορρόφηση ισχύος ολόκληρης της μεταγωγής.

11). Σχεδιασμός & υλοποίηση επεξεργαστή ρομπότ Ενεργοποιώντας την αντι-σύγκρουση με την τεχνολογία RFID

Το προτεινόμενο σύστημα χρησιμοποιείται κυρίως για την εφαρμογή ενός επεξεργαστή ρομπότ με αντι-σύγκρουση για να αποφευχθεί η φυσική σύγκρουση ρομπότ στο περιβάλλον των πολλαπλών ρομπότ. Αυτός ο αλγόριθμος εφαρμόζεται κυρίως χρησιμοποιώντας τεχνολογία VHDL & RFID.

12). Σχεδιασμός λογικού κυκλώματος με εξοικονόμηση ενέργειας χρησιμοποιώντας αδιαβατική μέθοδο

Αυτό το σύστημα επιδεικνύει το λογικό σχεδιασμό κυκλώματος με αποτελεσματική αδιαβατική μέθοδο σε σύγκριση με συμβατικό σχεδιασμό CMOS με τη βοήθεια κυκλωμάτων που χρησιμοποιούν Πύλες NAND & NOR . Με τη χρήση της αδιαβατικής μεθόδου, η απόρριψη ισχύος στο δίκτυο μπορεί να μειωθεί καθώς ανακυκλώνει την αποθηκευμένη ενέργεια εντός του πυκνωτή φορτίου.

3). Σύστημα κρυπτογράφησης για βελτίωση της ταχύτητας υπολογισμού του συστήματος

Ο κύριος σκοπός αυτού του έργου είναι η ενίσχυση της ασφάλειας μετάδοσης δεδομένων για τη βελτίωση της ταχύτητας των υπολογιστών εφαρμόζοντας τον αλγόριθμο του AES χρησιμοποιώντας το FPGA. Έτσι, αυτή η προσομοίωση, καθώς και ο μαθηματικός σχεδιασμός, μπορούν να πραγματοποιηθούν με τη βοήθεια του κώδικα VHDL.

14). Μπλοκ IP AHM ή Advanced High-Performance Bus

Αυτό το έργο χρησιμοποιείται κυρίως για το σχεδιασμό μιας αρχιτεκτονικής του Advanced Μικροελεγκτής Bus (AMB) χρησιμοποιώντας AHBN (Advanced High-Performance Bus). Αυτό το έργο μπορεί να σχεδιαστεί με κώδικα VHDL εφαρμόζοντας τα μπλοκ όπως το master & save.

15). Πομποδέκτης RF πολλαπλών τρόπων με βάση DSM με πολυκάναλο

Αυτό το σύστημα χρησιμοποιείται κυρίως για το σχεδιασμό μιας αρχιτεκτονικής πομπού & δέκτη πολλαπλών τρόπων και πολυκαναλικών RF με διαμορφωτή Delta-Sigma. Αυτό το προτεινόμενο σύστημα χρησιμοποιεί μια γλώσσα VHDL για την εφαρμογή δύο αρχιτεκτονικών.

16). Ο Συγκεντρωτής του Διακόπτη Knockout χρησιμοποιώντας μια Ασύγχρονη Λειτουργία Μεταφοράς

Με τη χρήση αυτού του έργου, ένας διακόπτης νοκ-άουτ που βασίζεται σε ασύγχρονη μεταφορά μπορεί να σχεδιαστεί με τη βοήθεια εργαλείων όπως τα VHS & VHDL. Αυτός ο διακόπτης νοκ-άουτ μπορεί να χρησιμοποιηθεί στα δίκτυα πακέτων εικονικών κυκλωμάτων, καθώς και σε εφαρμογές του datagram.

17). Συμπεριφορική σύνθεση ασύγχρονων κυκλωμάτων

Αυτό το έργο χρησιμοποιείται κυρίως για την παροχή της τεχνικής σύνθεσης συμπεριφοράς που χρησιμοποιείται για ασύγχρονα κυκλώματα. Και τα δύο πρότυπα όπως το balsa & οι ασύγχρονες υλοποιήσεις είναι τα κύρια στοιχεία του σχεδιασμού.

18). Σχεδιασμός AMBA με χρήση συμβατού ελεγκτή μνήμης AHB

Αυτό το έργο χρησιμοποιείται για το σχεδιασμό ενός MC (ελεγκτή μνήμης) ανάλογα με το AMBA (Advanced Microcontroller Bus Architecture) για τον έλεγχο της μνήμης του συστήματος χρησιμοποιώντας την κύρια μνήμη όπως το SRAM & ROM.

19). Εφαρμογή Carry Tree Adder

Το Carry Tree Adder με βάση το σχεδιασμό VLSI ονομάζεται ως το καλύτερο πρόσθετο απόδοσης σε αντίθεση με τα συνηθισμένα δυαδικά πρόσθετα. Τα πρόσθετα που υλοποιούνται από αυτό το έργο είναι το δέντρο, η πέτρα και η αραιή πέτρα.

20). CORDIC Περιστροφή σταθερής γωνίας με βάση το σχεδιασμό

Η κύρια ιδέα αυτού του προτεινόμενου συστήματος είναι η περιστροφή διανυσμάτων χρησιμοποιώντας σταθερές γωνίες. Αυτές οι γωνίες είναι απαραίτητες για παιχνίδια, ρομποτική, ΕΠΕΞΕΡΓΑΣΙΑ ΕΙΚΟΝΑΣ , κ.λπ. Με τη χρήση αυτού του έργου, η περιστροφή του φορέα μπορεί να επιτευχθεί χρησιμοποιώντας συγκεκριμένες γωνίες με το σχεδιασμό του CORDIC (ψηφιακός υπολογιστής περιστροφής συντεταγμένων).

21). Σχεδίαση φίλτρου FIR με κατανεμημένο αριθμητικό πίνακα αναζήτησης

Αυτό το προτεινόμενο σύστημα ενισχύει κυρίως Φίλτρο FIR απόδοση, σχεδιάζοντας τη χρησιμοποιώντας κατανεμημένη αριθμητική ενός τρισδιάστατου πίνακα αναζήτησης στη θέση του πολλαπλασιαστή. Έτσι, αυτός ο σχεδιασμός μπορεί να εφαρμοστεί χρησιμοποιώντας λογισμικά όπως FPGA & Xilinx.

22). Push-Pull Pulsed Latches με υψηλή ταχύτητα και χαμηλή ισχύ υπό όρους

Αυτό το έργο χρησιμοποιείται για την εκτέλεση ενεργειακά αποδοτικών και υψηλής απόδοσης παλμικών μανδάλων που χρησιμοποιούνται κυρίως για συστήματα VLSI χρησιμοποιώντας νέα τοπολογία. Επειδή αυτή η τοπολογία εξαρτάται κυρίως από ένα τελικό στάδιο που ωθείται με τράβηγμα χρησιμοποιώντας δύο διαχωριστικές λωρίδες μέσω μιας γεννήτριας παλμού υπό όρους.

23). Αρχιτεκτονική Coder VLSI Architecture στο SPIHT

Αυτό το προτεινόμενο σύστημα βελτιώνει την απόδοση της μεθόδου της αριθμητικής κωδικοποίησης στο σύνολο διαμερισμάτων σε ιεραρχικά δέντρα (SPIHT) συμπίεση εικόνας με την αρχιτεκτονική υψηλής ταχύτητας ανάλογα με το FPGA.

24). Καταστολή θορύβου σήματος ΗΚΓ με βάση FPGA

Αυτό το έργο χρησιμοποιείται για τον περιορισμό του θορύβου στα σήματα ΗΚΓ μέσω δύο μέσων φίλτρων με μεγέθη σημείου 91 & 7 αντίστοιχα. Έτσι, αυτή η διαδικασία μπορεί να επιτευχθεί με την εφαρμογή του Σχεδιασμός FPGA με βάση τον κώδικα VHDL.

25). Επεξεργαστής κλιμάκωσης εικόνας υψηλής απόδοσης με βάση το VLSI με χαμηλό κόστος

Αυτό το έργο χρησιμοποιείται για την εφαρμογή ενός αλγορίθμου για επεξεργαστή κλιμάκωσης εικόνας που βασίζεται σε VLSI με λιγότερη μνήμη και υψηλή απόδοση. Ο προτεινόμενος σχεδιασμός συστήματος περιλαμβάνει κυρίως συνδυασμό φίλτρων, επαναδιαμορφώσιμων δυναμικών μεθόδων και κοινής χρήσης υλικού για μείωση του κόστους.

26). Σχεδιασμός & Εφαρμογή Αρχιτεκτονικής του Systolic Array

Η κύρια ιδέα αυτού του έργου είναι να σχεδιάσει ένα μοντέλο υλικού που χρησιμοποιείται για τον πολλαπλασιαστή συστολικής συστοιχίας. Αυτός ο πίνακας μπορεί να χρησιμοποιηθεί κυρίως για την εκτέλεση δυαδικού πολλαπλασιασμού με τη βοήθεια της πλατφόρμας VHDL. Ο προτεινόμενος σχεδιασμός συστήματος μπορεί να εφαρμοστεί χρησιμοποιώντας λογισμικό FPGA & Isim.

27). Σχεδιασμός & Σύνθεση QPSK χρησιμοποιώντας κώδικα VHDL

QPSK είναι μια από τις κύριες μεθόδους διαμόρφωσης. Αυτή η μέθοδος χρησιμοποιείται στις εφαρμογές του δορυφορικού ραδιοφώνου. Αυτή η τεχνική διαμόρφωσης μπορεί να εφαρμοστεί μέσω αναστρέψιμων λογικών πυλών. Ο σχεδιασμός της τεχνικής QPSK μπορεί να γίνει με τη βοήθεια του κώδικα VHDL.

28). Σχεδιασμός & υλοποίηση ελεγκτή DDR SDRAM με υψηλή ταχύτητα

Το προτεινόμενο σύστημα χρησιμοποιείται για το σχεδιασμό ενός ελεγκτή DDR SDRAM για τη μεταφορά δεδομένων ριπής ανάλογα με την υψηλή ταχύτητα για συγχρονισμό αυτών των δεδομένων μεταξύ του κυκλώματος του ενσωματωμένου συστήματος & του DDR SDRAM. Χρησιμοποιώντας τη γλώσσα VHDL, ο κώδικας μπορεί να αναπτυχθεί.

29). Σχεδιασμός & υλοποίηση επεξεργαστή RISC 32-bit

Η βασική ιδέα αυτού του έργου είναι η υλοποίηση 32 bit RISC (Υπολογιστής σετ μειωμένων οδηγιών) με τη βοήθεια ενός εργαλείου όπως το XILINK VIRTEX4. Σε αυτό το έργο, 16 σύνολα εντολών σχεδιάζονται οπουδήποτε κάθε εντολή μπορεί να εκτελεστεί σε έναν μόνο κύκλο CLK χρησιμοποιώντας τη μέθοδο 5-φάσεων σωληνώσεων.

30). Εφαρμογή Bus Bridge μεταξύ AHB & OCP

Το προτεινόμενο σύστημα χρησιμοποιείται για το σχεδιασμό μιας γέφυρας διαύλου μεταξύ δύο πρωτοκόλλων, δηλαδή κοινών και τυπικών. Τα πρωτόκολλα επικοινωνίας όπως AHB (Advanced High-Performance Bus) & OCP (Open Core Protocol) είναι πολύ δημοφιλή τα οποία χρησιμοποιούνται στις εφαρμογές του SoC (Σύστημα On-chip) .

Ιδέες έργων VLSI για φοιτητές μηχανικής

Παρακάτω παρατίθεται η λίστα έργων VLSI που βασίζονται σε έργα FPGA, MatLab, IEEE και Mini για φοιτητές μηχανικής.

Έργα VLSI για μαθητές M. Tech

Ο κατάλογος των έργων VLSI που βασίζονται στο M. Tech Student περιλαμβάνει τα ακόλουθα.

- Σχεδιασμός κυψελών μνήμης I0T με βάση την αποτελεσματική και εξαιρετικά αξιόπιστη περιοχή RHBD που χρησιμοποιείται σε εφαρμογές αεροδιαστημικής

- Ανιχνευτής φάσης με πολύπλευρο μισό ρυθμό που χρησιμοποιείται για κυκλώματα ανάκτησης CLK & δεδομένων

- Συγκριτής με χαμηλή ισχύ και υψηλή ταχύτητα που χρησιμοποιείται για ακριβείς εφαρμογές

- Μεταφραστής Gated Level Voltage με υψηλής απόδοσης και ενσωματωμένο πολυπλέκτη

- Ternary Adder με βάση το CNTFET με υψηλή απόδοση

- Σχεδίαση Magnitude Comparator με χαμηλή ισχύ

- Σχεδιασμός Threshold Logic Gate με Τρέχουσα Λειτουργία για Ανάλυση Καθυστέρησης

- Σχεδιασμός αποκωδικοποιητών γραμμής μικτής λογικής με χαμηλή ισχύ και υψηλή απόδοση

- Σχεδιασμός λογικής δοκιμής Sleep Convention

- Μετατροπέας στάθμης τάσης για εφαρμογές διπλής τροφοδοσίας με υψηλή ταχύτητα και εξοικονόμηση ενέργειας

- Σχεδίαση & Ανάλυση Συγκριτών Χαμηλής Τάσης & Διπλής Ουράς Χαμηλής Τάσης

- Σχεδιασμός Flip-Flop βασισμένο σε Pulse-Triggered με χαμηλή ισχύ χρησιμοποιώντας μια μέθοδο τροφοδοσίας σήματος

- Αποτελεσματικός σχεδιασμός κυκλωμάτων βασισμένος σε RETime Reconfigurable FETs

- Σχεδίαση Magnitude Comparator με χαμηλή ισχύ

- Ανάλυση Καθυστέρησης Σχεδίων Λογικής Πύλης με Όριο Τρέχουσας Λειτουργίας

ο Έργα VLSI που βασίζονται σε FPGA για φοιτητές μηχανικής και Μικρά έργα σχεδιασμού CMOS VLSI αναφέρονται παρακάτω.

- Σχεδιασμός & Χαρακτηρισμός σκληρυμένων κυκλωμάτων SEU για FPGA με βάση SRAM

- Μια υβριδική εφαρμογή LUT Design & Potential CMOS με βάση το Compact Memristor που χρησιμοποιείται στο FPGA

- Υλοποίηση υπερήχων με βάση αισθητήρα FPGA για μέτρηση απόστασης

- Εφαρμογή FPGA για Booth Multiplier με Spartan6 FPGA

- Διακριτός μετασχηματισμός Wavelet με βάση την ανύψωση με Spartan3 FPGA

- ARM Controller in Robotics χρησιμοποιώντας FPGA

- UART βασισμένο σε FPGA με πολυκάναλο

- Καταστολή θορύβου σήματος ΗΚΓ με χρήση FPGA

- Εφαρμογή FPGA με βάση UTMI & στρώμα πρωτοκόλλου USB 2.0

- Υλοποίηση μέσου φίλτρου με Spartan3 FPGA

- Εφαρμογή FPGA με βάση τον αλγόριθμο AES

- Σύστημα ειδοποίησης ασφαλείας βασισμένο σε PIC για την εφαρμογή του FPGA με το Spartan 3an

- Εφαρμογή FPGA για το σχεδιασμό του ελεγκτή για συστήματα τηλεπισκόπησης

- Κιτ επεξεργασίας εικόνων του FPGA χρησιμοποιώντας φιλτράρισμα εικόνων γραμμικής και μορφολογικής

- Εφαρμογή ιατρικής σύντηξης με βάση το Spartan3 FPGA

Ο κατάλογος των Τα μίνι έργα VLSI χρησιμοποιούν κώδικα VHDL περιλαμβάνει τα ακόλουθα.

- Συγκριτής με υψηλή ταχύτητα χρησιμοποιώντας VLSI

- Πολλαπλασιαστής Floating-Point χρησιμοποιώντας VLSI

- Μετατροπή του δυαδικού σε γκρι με βάση το VLSI

- Ψηφιακό φίλτρο

- CLK Gating με βάση το VLSI

- Βεδικός πολλαπλασιαστής

- CMOS FF χρησιμοποιώντας VLSI

- Η αρχιτεκτονική του Parallel Processor χρησιμοποιώντας VLSI

- Πλήρης προσθήκη με βάση το VLSI

- Σχεδιασμός μνήμης DRAM / Dynamic Random Access βάσει VLSI

- Διάταξη SRAM με βάση το VLSI

- Επεξεργαστής ψηφιακού σήματος με βάση το VLSI

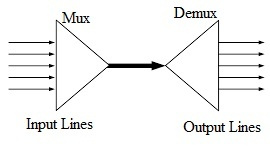

- Πολυπλέκτης με βάση το VLSI

- Σχεδιασμός μονάδας MAC με βάση το VLSI

- Διαφορετικός με βάση το VLSI

- Βασισμένο σε VLSI FFT ή Fast Fourier Transform

- Η αρχιτεκτονική του Discrete Cosine Transform βασίζεται στο VLSI

- Σχεδιασμός πολλαπλασιαστή 16-bit με χρήση VLSI19

- Σχεδιασμός βασισμένος στο VLSI του FIFO Buffer

- Επιταχυντής υψηλής ταχύτητας με βάση το VLSI

Έργα VLSI με χρήση MATLAB & Xilinx

Η λίστα των έργων VLSI που βασίζονται σε έργα MATLAB και VLSI που χρησιμοποιούν το Xilinx περιλαμβάνει τα ακόλουθα.

- Σχεδίαση & ανάλυση μόντεμ CDMA με MATLAB

- Σχεδίαση φίλτρου FIR με χρήση VHDL σε ανάλυση με βάση FPGA & MATLAB

- Model Sim & Matlab ή Simulink Simulation of System for Automotive Engineering

- Πρόσθετα με βάση το Xilinx όπως το Ripple Carry & Carry Skip

- Αριθμητική μονάδα βασισμένη σε 32-bit Floating Point

- Κινούμενο σημείο με βάση ALU

- Επεξεργαστής RISC με βάση 32-bit

- Δυνατότητες σύγκλισης του ορθογώνιου κώδικα

- Μηχάνημα αυτόματης πώλησης με βάση το Xilinx και το Verilog

- Πρόσθετοι παράλληλοι πρόθετοι με βάση το Xilinx με 256-bit

- Πρωτόκολλο για αμοιβαίο έλεγχο ταυτότητας με χρήση του Xilinx

- Δομή πρόσβασης με έναν κύκλο για δοκιμή λογικής χρησιμοποιώντας Xilinx

- UTMI & Protocol Layer με βάση USB2.0 χρησιμοποιώντας Xilinx

- Διαμόρφωση συμπίεσης δεδομένων και αποσυμπίεσης χρησιμοποιώντας Xilinx FPGA

- Xilinx 4000 με βάση BIST & Spartan Series FPGAs

- Φίλτρο IIR με βάση MATLAB & VLSI

- Φίλτρο FIR με χρήση MATLAB

Έργα IEEE

ο λίστα έργων IEEE VLSI παρατίθεται παρακάτω.

- Σύστημα ασύρματου οικιακού αυτοματισμού που βασίζεται σε VLSI χρησιμοποιώντας Bluetooth

- Αφαίρεση του παλμού θορύβου μέσα στην εικόνα χρησιμοποιώντας μια αποτελεσματική αρχιτεκτονική του VLSI

- Η αρχιτεκτονική ενός επεξεργαστή σε μνήμη για συμπίεση πολυμέσων

- Παρακολούθηση του συστήματος θερμοκρασίας με χρήση Cloud & IoT

- Υλοποίηση συστήματος OFDM με IFFT & FFT

- Σχεδιασμός & υλοποίηση κώδικα Hamming με το Verilog

- Αναγνώριση δακτυλικών αποτυπωμάτων με βάση το VHDL χρησιμοποιώντας το φίλτρο Gabor

- Ανακατασκευή αριθμητικών λειτουργιών με ROM ανάλογα με τις προσεγγίσεις προσέγγισης

- Ανάλυση της Απόδοσης Υψηλής Απόδοσης & Χαμηλής Πυκνότητας του Κωδικού Αποκωδικοποιητή Ελέγχου Ισοτιμίας σε Εφαρμογές Χαμηλής Ισχύος

- Αρχιτεκτονικές FFT με Feedforward of Pipelined Radix-2k

- Σχεδιασμός Flip-Flops για εφαρμογές VLSI χρησιμοποιώντας τεχνολογία CMOS με υψηλή απόδοση

- Σχεδίαση φίλτρου FIR με πίνακα αναζήτησης κατά κατανεμημένη αριθμητική

- Επεξεργαστής χαμηλού κόστους & βελτιωμένης κλιμάκωσης εικόνας με βάση το VLSI

- ASIC Εφαρμογή & Σχεδιασμός ενός Advance Turbo Encoder & Decoder με 3GPP LTE

- Push-Pull Pulsed μάνδαλα με χαμηλή ισχύ και υψηλή ταχύτητα υπό όρους

- Βελτιωμένη σάρωση σε δοκιμές σάρωσης χαμηλής ισχύος

- Αρχιτεκτονική Coder VLSI Architecture για SPIHT

- Εφαρμογή VHDL για UART

- Ρυθμιστής τάσης με βάση το VLSI με χαμηλή πτώση

- Σχεδιασμός Flash ADC με ενισχυμένο συγκριτικό σχήμα

- Σχεδιασμός πολλαπλασιαστή χαμηλής ισχύος με στυλ λογικής σταθερής καθυστέρησης

- Συγκριτής διπλής ουράς με υψηλή απόδοση και χαμηλή ισχύ

- Σύστημα αποθήκευσης Flash με υψηλή απόδοση, ανάλογα με το buffer εγγραφής και την εικονική μνήμη

- Χαμηλή ισχύ FF με βάση την προσέγγιση Sleepy Stack

- Βελτιστοποίηση ισχύος LFSR για BIST χαμηλής ισχύος Εφαρμογή σε HDL

- Σχεδιασμός και υλοποίηση αυτόματου πωλητή με Verilog HDL

- Σχεδιασμός συσσωρευτή με βάση τη δημιουργία μοτίβου 3-βάρους με LP-LSFR

- Αποκωδικοποιητής Reed-Solomon με υψηλή ταχύτητα και χαμηλή πολυπλοκότητα

- Ταχύτερη τεχνική σχεδιασμού πολλαπλασιαστή Dadda

- Ψηφιακός αποδιαμορφωτής δέκτης ραδιοφώνου FM

- Δημιουργία μοτίβου δοκιμής με σχήματα BIST

- Υλοποίηση της αρχιτεκτονικής VLSI με αγωγούς υψηλής ταχύτητας

- Σχεδιασμός πρωτοκόλλου On-Chip Bus OCP χρησιμοποιώντας λειτουργίες Bus

- Σχεδιασμός Ανιχνευτή Συχνότητας Φάσης & Αντλία Φόρτισης που χρησιμοποιείται για βρόχο κλειδώματος φάσης υψηλής συχνότητας

- Cache Memory & Cache Controller Design με VHDL

- Εφαρμογή με βάση την ASTRAN Συμπιεστές χαμηλής ισχύος 3-2 & 4-2

- Προπληρωμένο σύστημα χρέωσης ηλεκτρικού ρεύματος με χρήση On-Chip Design

- Υλοποίηση αλληλεπικάλυψης με χρήση του κελιού λογικής και της ανάλυσης ισχύος του

- Carry Look Ahead Adder με διαφορετική ανάλυση απόδοσης bit χρησιμοποιώντας VHDL

- Σχεδιασμός επιπέδου συνδέσμου δεδομένων με Wi-Fi MAC Πρωτόκολλα

- Εφαρμογή FPGA για πρωτόκολλο αμοιβαίου ελέγχου ταυτότητας με αρθρωτή αριθμητική

- Δημιουργία σήματος PWM με χρήση FPGA & Variable Duty Cycle

Έργα σε πραγματικό χρόνο

Ο κατάλογος των Έργα VLSI σε πραγματικό χρόνο περιλαμβάνουν κυρίως έργα VLSI mini που χρησιμοποιούν κώδικα VHDL και προγράμματα λογισμικού VLSI για μαθητές μηχανικής ECE.

- Πραγματική ενσωμάτωση SRAM Row Cache στην ετερογενή 3-D DRAM αρχιτεκτονική με χρήση TSV

- Ενσωματωμένη τεχνική αυτοελέγχου για τη διάγνωση σφαλμάτων καθυστέρησης σε προγραμματιζόμενες συστοιχίες πυλών με βάση το πεδίο

- ASIC Σχεδιασμός σύνθετου πολλαπλασιαστή

- Εφαρμογή χαμηλού κόστους VLSI για αποτελεσματική απομάκρυνση του παλμού

- Βασισμένο σε FPGA Space Vector PWM IC ελέγχου για τριφασικό επαγωγικό κινητήρα

- Εφαρμογή VLSI του αυτόματου συσχετιστή και του αλγόριθμου CORDIC για WLAN βάσει OFDM

- Αυτόματη εξαγωγή δρόμου χρησιμοποιώντας δορυφορικές εικόνες υψηλής ανάλυσης

- Σχεδιασμός VHDL για τμηματοποίηση εικόνας χρησιμοποιώντας φίλτρο Gabor για ανίχνευση ασθενειών

- Μια αρχιτεκτονική Turbo Decoder χαμηλής πολυπλοκότητας για ενεργειακά αποδοτικά ασύρματα δίκτυα αισθητήρων

- Βελτίωση των δυνατοτήτων σύγκλισης ορθογώνιου κώδικα με χρήση της εφαρμογής FPGA

- Σχεδιασμός και υλοποίηση ALU Floating Point

- CORDIC Σχεδιασμός για σταθερή γωνία περιστροφής

- Product Reed-Solomon Codes για την εφαρμογή NAND Flash Controller σε FPGA Chip

- Βελτίωση απόδοσης απόδοσης στατιστικών SRAM με χρήση κυκλωμάτων αρνητικής χωρητικότητας

- Διαχείριση ισχύος των διασυνδέσεων δικτύου MIMO σε κινητά συστήματα

- Σχεδιασμός προτύπου κρυπτογράφησης δεδομένων για κρυπτογράφηση δεδομένων

- Χαμηλής ισχύος και αποδοτική περιοχή μεταφοράς Επιλέξτε Adder

- Σύνθεση και εφαρμογή UART με χρήση κωδικών VHDL

- Βελτιωμένες αρχιτεκτονικές για μια μονάδα αφαίρεσης αιωρούμενου σημείου Fused Floating Point

- Ένας ψηφιακός πομπός 1-bit που βασίζεται σε FPGA που χρησιμοποιεί διαμόρφωση Delta-Sigma με έξοδο RF για SDR

- Βελτιστοποίηση χρήσης αναζήτησης αλυσίδας στον αποκωδικοποιητή BCH για μετάδοση υψηλού ποσοστού σφαλμάτων

- Ψηφιακός σχεδιασμός πομπού DS-CDMA με χρήση Verilog HDL και FPGA

- Σχεδιασμός και υλοποίηση αποτελεσματικής αρχιτεκτονικής συστολικής συστοιχίας

- Ένας αλγόριθμος εκμάθησης ρομποτικής δυναμικής που βασίζεται σε VLSI

- Ένας ευέλικτος σχεδιασμός λειτουργικών μονάδων πολυμέσων που χρησιμοποιεί την τεχνική ψευδούς καταστολής ισχύος

- Σχεδιασμός γέφυρας λεωφορείων μεταξύ AHB και OCP

- Συμπεριφορική σύνθεση ασύγχρονων κυκλωμάτων

- Βελτιστοποίηση ταχύτητας ενός τροποποιημένου Viterbi Decoder βάσει FPGA

- Εφαρμογή διασύνδεσης I2C

- Ένας πολλαπλασιαστής υψηλής ταχύτητας / χαμηλής ισχύος χρησιμοποιώντας μια προηγμένη τεχνική καταστολής ψευδούς ισχύος

- Σύσφιξη εικονικής τάσης τροφοδοσίας κυκλωμάτων ισχύος για ενεργή μείωση διαρροής και αξιοπιστία οξειδίου πύλης

- FPGA Based Power Efficient Channelizer για ραδιόφωνο που καθορίζεται από λογισμικό

- VLSI Architecture και FPGA Prototyping of a Digital Camera for Image Security and Authentication

- Βελτίωση λειτουργίας εσωτερικού ρομπότ

- Σχεδιασμός και υλοποίηση ενός δικτύου μετατροπής ON-Chip για σύστημα πολλαπλών επεξεργαστών-On-Chip

- Μέθοδος συγχρονισμού συγχρονισμού ρυθμού συμβόλων για ασύρματα συστήματα OFDM χαμηλής ισχύος

- DMA Controller (Direct Memory Access) Χρησιμοποιώντας VHDL / VLSI

- Αναδιαμορφώσιμο FFT χρησιμοποιώντας αρχιτεκτονική βασισμένη σε CORDIC για δέκτες MIMI-OFDM

- Τεχνική ψευδούς καταστολής ισχύος για εφαρμογές πολυμέσων / DSP

- Η αποτελεσματικότητα των κωδικών BCH στο Digital Image Watermarking

- Διπλός ρυθμός δεδομένων SD-RAM Controller

- Εφαρμογή φίλτρου Gabor για αναγνώριση δακτυλικών αποτυπωμάτων με χρήση Verilog HDL

- Σχεδιασμός Πρακτικής Πλεονάζουσας Κλίμακας Νανομέτρων μέσω Aware Standard Cell Library για Βελτιωμένο Πλεονάζον μέσω 1 Ρυθμού Εισαγωγής

- Ένας αλγόριθμος συμπίεσης και αποσυμπίεσης δεδομένων χωρίς απώλεια και η αρχιτεκτονική του υλικού

- Ένα πλαίσιο για τη διόρθωση πολλαπλών σφαλμάτων πολλαπλών bit

- Αποτελεσματική συμπίεση δεδομένων δοκιμής με βάση Viterbi

- Υλοποίηση των μπλοκ FFT / IFFT για OFDM

- Συμπίεση εικόνας βασισμένη σε Wavelet από VLSI Progressive Coding

- VLSI Υλοποίηση Πλήρως Συνδεδεμένου Πολλαπλασιαστή Λιγότερο 2D DCT / IDCT Architecture για Jpeg

- Προσομοίωση σφαλμάτων βασισμένων σε FPGA συγχρονισμένων διαδοχικών κυκλωμάτων

Έτσι, όλα αυτά αφορούν τη λίστα έργων VLSI για μηχανικούς, μαθητές M.Tech που βοηθούν στην επιλογή του θέματος του τελικού έτους. Αφού ξοδέψατε τον πολύτιμο χρόνο σας κατά τη διάρκεια αυτής της λίστας, πιστεύουμε ότι έχετε μια αρκετά καλή ιδέα να επιλέξετε το θέμα του έργου της επιλογής σας από τη λίστα έργων VLSI και ελπίζουμε ότι έχετε αρκετή αυτοπεποίθηση για να αναλάβετε οποιοδήποτε θέμα από το λίστα. Για περισσότερες λεπτομέρειες και βοήθεια με αυτά τα έργα, μπορείτε να μας γράψετε στην ενότητα σχολίων που δίνεται παρακάτω. Εδώ είναι μια ερώτηση για εσάς, τι είναι το VHDL;

Δικαιώματα φωτογραφίας

- Έργα VLSI από σύνολο τεχνολογίας