Στον τομέα των ηλεκτρονικών, η πιο κρίσιμη ιδέα στην οποία λειτουργεί κάθε στοιχείο είναι το « Λογικές πύλες '. Καθώς η έννοια των λογικών πυλών εφαρμόζεται σε κάθε λειτουργικότητα, όπως σε ολοκληρωμένα κυκλώματα, αισθητήρες, σκοπούς μεταγωγής, μικροελεγκτές και επεξεργαστές, σκοπούς κρυπτογράφησης και αποκρυπτογράφησης και άλλα. Εκτός από αυτά, υπάρχουν πολλές εφαρμογές της Logic Gates. Υπάρχουν πολλοί τύποι λογικών πυλών όπως Adder, Subtractor, Full Αθροιστής , Full Subtractor, Half Subtractor και πολλά άλλα. Έτσι, αυτό το άρθρο παρέχει συλλογικές πληροφορίες για κύκλωμα μισού αφαίρεσης , μισός πίνακας αλήθειας αφαίρεσης και συναφείς έννοιες.

Τι είναι το Half Subtractor;

Πριν πάμε να συζητήσουμε το μισό αφαίρεση, πρέπει να γνωρίζουμε τη δυαδική αφαίρεση. Στη δυαδική αφαίρεση, η διαδικασία αφαίρεσης είναι παρόμοια με την αριθμητική αφαίρεση. Στην αριθμητική αφαίρεση χρησιμοποιείται το σύστημα αριθμών βάσης 2 ενώ στην δυαδική αφαίρεση, χρησιμοποιούνται δυαδικοί αριθμοί για αφαίρεση. Οι προκύπτοντες όροι μπορούν να δηλωθούν με τη διαφορά και να δανειστούν.

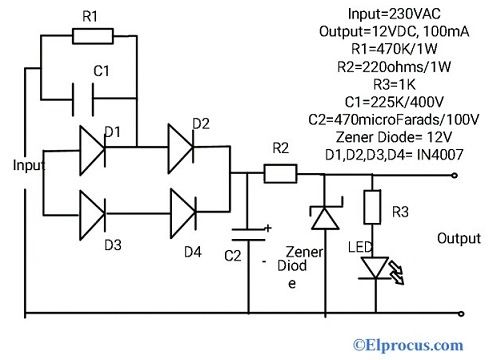

Το μισό αφαίρεσης είναι το πιο σημαντικό συνδυαστικό λογικό κύκλωμα που χρησιμοποιείται στο ψηφιακά ηλεκτρονικά . Βασικά, πρόκειται για ηλεκτρονική συσκευή ή με άλλους όρους, μπορούμε να το πούμε ως λογικό κύκλωμα. Αυτό το κύκλωμα χρησιμοποιείται για την εκτέλεση αφαίρεσης δυαδικών ψηφίων. Στο προηγούμενο άρθρο, έχουμε ήδη συζητήσει τις έννοιες του μισού αθροιστή και ενός πλήρους κύκλου αθροιστών που χρησιμοποιεί δυαδικούς αριθμούς για τον υπολογισμό. Παρομοίως, το κύκλωμα αφαίρεσης χρησιμοποιεί δυαδικούς αριθμούς (0,1) για την αφαίρεση. Το κύκλωμα του μισού αφαίρεσης μπορεί να κατασκευαστεί με δύο λογικές πύλες, οι πύλες NAND και EX-OR . Αυτό το κύκλωμα δίνει δύο στοιχεία όπως η διαφορά καθώς επίσης και δανείζονται.

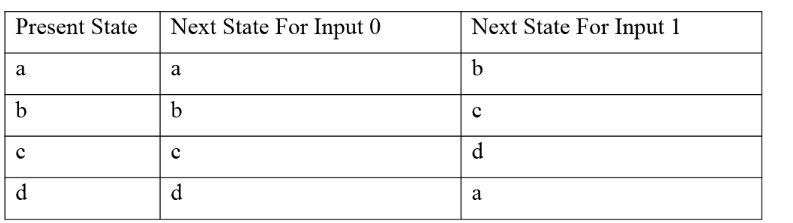

Όπως και στη δυαδική αφαίρεση, το κύριο ψηφίο είναι 1, μπορούμε να δημιουργήσουμε δανεισμό, ενώ η δευτερεύουσα τάση 1 είναι ανώτερη από το minuend 0 και λόγω αυτού, θα χρειαστεί δανεισμός. Το ακόλουθο παράδειγμα δίνει τη δυαδική αφαίρεση δύο δυαδικών δυαδικών ψηφίων.

Πρώτο ψηφίο | Δεύτερο ψηφίο | Διαφορά | Δανείζομαι |

0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

Στην παραπάνω αφαίρεση, τα δύο ψηφία μπορούν να αναπαρασταθούν με τα Α και Β. Αυτά τα δύο ψηφία μπορούν να αφαιρεθούν και δίνουν τα προκύπτοντα ψηφία ως διαφορά και δανεισμό.

Όταν παρατηρούμε τις πρώτες δύο και τέταρτες σειρές, η διαφορά μεταξύ αυτών των σειρών, τότε η διαφορά και ο δανεισμός είναι παρόμοια, επειδή το δευτερεύον τραχύ είναι μικρότερο από το minuend. Ομοίως, όταν παρατηρούμε την τρίτη σειρά, η τιμή minuend αφαιρείται από το subtrahend. Επομένως, η διαφορά και το bit δανεισμού είναι 1 επειδή το ψηφίο δευτερεύοντος τραγουδιού είναι ανώτερο από το ψηφίο minuend.

Αυτό το συνδυαστικό κύκλωμα είναι ένα ουσιαστικό εργαλείο για κάθε είδους ψηφιακό κύκλωμα να μάθουμε τους πιθανούς συνδυασμούς εισόδων και εξόδων. Για παράδειγμα, εάν ο αφαιρέτης έχει δύο εισόδους, τότε οι προκύπτουσες έξοδοι θα είναι τέσσερις. Το o / p του μισού αφαιρέτη αναφέρεται στον παρακάτω πίνακα που θα δηλώνει το bit διαφοράς καθώς και το bit δανεισμού. Η εξήγηση του πίνακα αλήθειας του κυκλώματος μπορεί να γίνει χρησιμοποιώντας τις πύλες λογικής όπως η λογική πύλη EX-OR και η λειτουργία πύλης AND ακολουθούμενη από την πύλη NOT.

Επίλυση του πίνακα αλήθειας χρησιμοποιώντας Κ-χάρτης φαίνεται παρακάτω.

μισός χάρτης αφαίρεσης

ο μισή έκφραση αφαίρεσης χρησιμοποιώντας τον πίνακα αλήθειας και το K-map μπορεί να εξαχθεί ως

Διαφορά (Δ) = ( είμαι + xy »)

= x ⊕ ε

Δανεισμός (B) = x'y

Λογικό κύκλωμα

ο λογικό κύκλωμα μισού αφαίρεσης μπορεί να εξηγηθεί χρησιμοποιώντας τις λογικές πύλες:

- 1 πύλη XOR

- 1 ΟΧΙ πύλη

- 1 ΚΑΙ πύλη

Η αναπαράσταση είναι

Λογικό κύκλωμα μισού αφαίρεσης

Διάγραμμα μπλοκ μισού-αφαιρετή

Το μπλοκ διάγραμμα του μισού αφαίρεσης φαίνεται παραπάνω. Απαιτεί δύο εισόδους καθώς και δύο εξόδους. Εδώ οι είσοδοι αντιπροσωπεύονται με A&B και οι έξοδοι είναι Difference and Borrow.

Το παραπάνω κύκλωμα μπορεί να σχεδιαστεί με πύλες EX-OR & NAND. Εδώ, η πύλη NAND μπορεί να κατασκευαστεί χρησιμοποιώντας πύλες AND και NOT. Επομένως, απαιτούμε τρεις λογικές πύλες για την κατασκευή μισού κυκλώματος αφαίρεσης, δηλαδή την πύλη EX-OR, την πύλη NOT και την πύλη NAND.

Ένας συνδυασμός πύλης AND και NOT παράγει μια διαφορετική συνδυασμένη πύλη που ονομάζεται NAND Gate. Η έξοδος πύλης Ex-OR θα είναι το bit διαφοράς και η έξοδος NAND Gate θα είναι το bit δανεισμού για τις ίδιες εισόδους A&B.

ΚΑΙ-Πύλη

Η πύλη AND είναι ένας τύπος ψηφιακής πύλης λογικής με πολλαπλές εισόδους και μία έξοδο και με βάση τους συνδυασμούς εισόδων θα εκτελέσει τη λογική σύζευξη. Όταν όλες οι είσοδοι αυτής της πύλης είναι υψηλές, τότε η έξοδος θα είναι υψηλή, διαφορετικά η έξοδος θα είναι χαμηλή. Το λογικό διάγραμμα της πύλης AND με τον πίνακα αλήθειας φαίνεται παρακάτω.

Πίνακας Πύλης και Αλήθειας

ΟΧΙ Πύλη

Η πύλη NOT είναι ένας τύπος πύλης ψηφιακής λογικής με μία είσοδο και με βάση την είσοδο, η έξοδος θα αντιστραφεί. Για παράδειγμα, όταν η είσοδος της πύλης NOT είναι υψηλή, τότε η έξοδος θα είναι χαμηλή. Το λογικό διάγραμμα του NOT-gate με τον πίνακα αλήθειας φαίνεται παρακάτω. Χρησιμοποιώντας αυτόν τον τύπο πύλης λογικής, μπορούμε να εκτελέσουμε πύλες NAND και NOR.

ΔΕΝ Πίνακας Πύλης και Αλήθειας

Ex-OR Gate

Η πύλη Exclusive-OR ή EX-OR είναι ένας τύπος πύλης ψηφιακής λογικής με 2 εισόδους και μία έξοδο. Η λειτουργία αυτής της λογικής πύλης εξαρτάται από την πύλη OR. Εάν κάποια από τις εισόδους αυτής της πύλης είναι υψηλή, τότε η έξοδος της πύλης EX-OR θα είναι υψηλή. Ο πίνακας συμβόλων και αλήθειας του EX-OR φαίνεται παρακάτω.

Πίνακας XOR Gate και Truth

Κύκλωμα μισού αφαίρεσης χρησιμοποιώντας πύλη Nand

Ο σχεδιασμός του αφαίρεσης μπορεί να γίνει από χρησιμοποιώντας λογικές πύλες όπως η πύλη NAND & η πύλη Ex-OR. Για να σχεδιάσουμε αυτό το κύκλωμα μισού αφαίρεσης, πρέπει να γνωρίζουμε τις δύο έννοιες, δηλαδή τη διαφορά και τον δανεισμό.

Κύκλωμα μισού αφαίρεσης χρησιμοποιώντας πύλη Nand

Εάν παρακολουθούμε προσεκτικά, είναι αρκετά σαφές ότι η ποικιλία λειτουργίας που εκτελείται από αυτό το κύκλωμα που σχετίζεται με ακρίβεια με τη λειτουργία πύλης EX-OR. Επομένως, μπορούμε απλά να χρησιμοποιήσουμε την πύλη EX-OR για να κάνουμε τη διαφορά. Με τον ίδιο τρόπο, το δάνειο που παράγεται από το κύκλωμα μισού αθροιστή μπορεί απλά να επιτευχθεί χρησιμοποιώντας το μείγμα των λογικών πυλών όπως η πύλη AND και η πύλη NOT.

Αυτό το HS μπορεί επίσης να σχεδιαστεί χρησιμοποιώντας πύλες NOR όπου απαιτούνται 5 πύλες NOR για την κατασκευή. Το μισό αφαίρεση του διαγράμματος κυκλώματος χρησιμοποιώντας πύλες NOR εμφανίζεται ως:

Μισή αφαίρεση που χρησιμοποιεί Nor Gates

Πίνακας αλήθειας

Πρώτο κομμάτι | Δεύτερο κομμάτι | Διαφορά (EX-OR Out) | Δανείζομαι (NAND Out) |

0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

VHDL και Testbench Code

Ο κώδικας VHDL για το μισό αφαίρεσης εξηγείται ως εξής:

βιβλιοθήκη IEEE

χρησιμοποιήστε το IEEE.STD_LOGIC_1164.ALL

χρησιμοποιήστε το IEEE.STD_LOGIC_ARITH.ALL

χρησιμοποιήστε το IEEE.STD_LOGIC_UNSIGNED.ALL

οντότητα Half_Sub1 είναι

Θύρα (a: στο STD_LOGIC

β: στο STD_LOGIC

HS_Diff: έξω STD_LOGIC

HS_Δάνειο: έξω STD_LOGIC)

τέλος Half_Sub1

αρχιτεκτονική Behavioral of Half_Sub1 είναι

να αρχίσει

HS_Diff<=a xor b

HS_Δάνειο<=(not a) and b

ο κωδικός δοκιμαστικού πάγκου για HS εξηγείται ως εξής:

ΒΙΒΛΙΟΘΗΚΗ IEEE

ΧΡΗΣΗ ieee.std_logic_1164.ALL

ENTITY HS_tb ΕΙΝΑΙ

ΤΕΛΟΣ HS_tb

ΑΡΧΙΤΕΚΤΟΝΙΚΗ HS_tb OF HS_tb IS

ΣΥΣΤΑΤΙΚΟ ΕΣ

Θύρα (a: IN std_logic

β: IN std_logic

HS_Diff: OUT std_logic

HS_Borrow: OUT std_logic

)

ΤΕΛΟΣ ΣΥΣΤΑΤΙΚΟ

σήμα a: std_logic: = ‘0’

σήμα b: std_logic: = ‘0’

σήμα HS_Diff: std_logic

σήμα HS_Borrow: std_logic

ΝΑ ΑΡΧΙΣΕΙ

νέο: ΧΑΡΤΗΣ ΛΙΜΑΝΙ HS (

α => α,

b => β,

HS_Diff => HS_Diff,

HS_borrow => HS_borrow

)

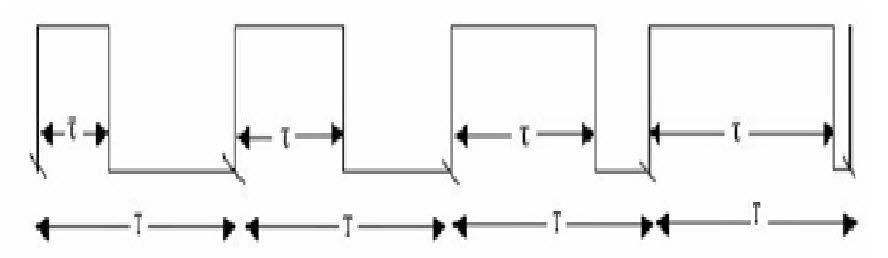

stim_proc: διαδικασία

να αρχίσει

προς την<= ‘0’

σι<= ‘0’

περιμένετε 30 ns

προς την<= ‘0’

σι<= ‘1’

περιμένετε 30 ns

προς την<= ‘1’

σι<= ‘0’

περιμένετε 30 ns

προς την<= ‘1’

σι<= ‘1’

Περίμενε

τελική διαδικασία

ΤΕΛΟΣ

Πλήρης αφαίρεση με χρήση μισού αφαίρεσης

Ένας πλήρης αφαίρεση είναι μια συνδυαστική συσκευή που λειτουργεί τη λειτουργικότητα αφαίρεσης χρησιμοποιώντας δύο bits και είναι minuend και subtrahend. Το κύκλωμα θεωρεί ότι δανείζεται την προηγούμενη έξοδο και έχει τρεις εισόδους με δύο εξόδους. Οι τρεις εισόδους είναι το minuend, subtrahend και η είσοδος που λαμβάνεται από την προηγούμενη έξοδο που είναι δανεισμός και οι δύο έξοδοι είναι η διαφορά και δανεισμός.

Πλήρες λογικό διάγραμμα αφαίρεσης

Ο πίνακας αλήθειας για πλήρης αφαίρεση είναι

| Είσοδοι | Έξοδοι | |||

| Χ | Γ | Γιν | FS_Diff | FS_Δάνειο |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Με τον παραπάνω πίνακα αλήθειας, το λογικό διάγραμμα κυκλωμάτων διαφημίσεων για την υλοποίηση του πλήρους αφαιρέτη με τη χρήση μισών αφαιρετών φαίνεται παρακάτω:

Πλήρης αφαίρεση με χρήση HS

Πλεονεκτήματα και περιορισμοί του μισού αφαιρέτη

Τα πλεονεκτήματα του μισού αφαίρεσης είναι:

- Η υλοποίηση και η κατασκευή αυτού του κυκλώματος είναι απλή και εύκολη

- Αυτό το κύκλωμα καταναλώνει ελάχιστη ισχύ στην επεξεργασία ψηφιακού σήματος

- υπολογιστικές λειτουργίες μπορούν να εκτελεστούν με βελτιωμένους ρυθμούς ταχύτητας

Οι περιορισμοί αυτού του συνδυαστικού κυκλώματος είναι:

Παρόλο που υπάρχουν εκτεταμένες εφαρμογές μισού αφαιρέτη σε πολλές λειτουργίες και λειτουργίες, υπάρχουν μερικοί περιορισμοί και αυτοί είναι:

- Τα κυκλώματα μισού αφαίρεσης δεν θα δεχτούν 'Borrow-in' από τις προηγούμενες εξόδους όπου αυτό είναι το κρίσιμο μειονέκτημα αυτού του κυκλώματος

- Καθώς πολλές εφαρμογές σε πραγματικό χρόνο λειτουργούν με την αφαίρεση πολλών αριθμών bits, οι συσκευές μισών αφαιρέσεων δεν έχουν καμία ικανότητα αφαίρεσης πολλών bits

Εφαρμογές του Half Subtractor

Οι εφαρμογές της μισής αφαίρεσης περιλαμβάνουν τα ακόλουθα.

- Η μισή αφαίρεση χρησιμοποιείται για τη μείωση της ισχύος των σημάτων ήχου ή ραδιοφώνου

- Μπορεί να είναι χρησιμοποιείται σε ενισχυτές για τη μείωση της παραμόρφωσης του ήχου

- Η μισή αφαίρεση είναι χρησιμοποιείται σε ALU του επεξεργαστή

- Μπορεί να χρησιμοποιηθεί για την αύξηση και μείωση των τελεστών και επίσης υπολογίζει τις διευθύνσεις

- Η μισή αφαίρεση χρησιμοποιείται για την αφαίρεση των λιγότερο σημαντικών αριθμών στηλών. Για την αφαίρεση πολυψήφων αριθμών, μπορεί να χρησιμοποιηθεί για το LSB.

Επομένως, από την παραπάνω θεωρία μισού αφαίρεσης, επιτέλους, μπορούμε να κλείσουμε ότι χρησιμοποιώντας αυτό το κύκλωμα μπορούμε να αφαιρέσουμε από ένα δυαδικό bit από το άλλο για να παρέχουμε τις εξόδους όπως το Difference and Borrow. Παρομοίως, μπορούμε να σχεδιάσουμε το μισό αφαίρεση χρησιμοποιώντας το κύκλωμα πύλης NAND καθώς και τις πύλες NOR. Οι άλλες έννοιες που πρέπει να είναι γνωστές είναι τι είναι μισός αφαιρετικός κωδικός verilog και πώς μπορεί να σχεδιαστεί το σχηματικό διάγραμμα RTL;