Το JTAG (Joint Test Action Group) είναι ένα καθιερωμένο πρότυπο IEEE 1149.1 που αναπτύχθηκε το έτος 1980 για να λύσει τα ζητήματα κατασκευής που προέκυψαν σε ηλεκτρονικές πλακέτες ή πλακέτες τυπωμένων κυκλωμάτων . Αυτή η τεχνολογία χρησιμοποιείται για την παροχή αρκετής δοκιμαστικής πρόσβασης για κάθε σύνθετη πλακέτα όταν η δοκιμαστική πρόσβαση μειώνεται. Έτσι, κυκλοφόρησε η τεχνολογία σάρωσης ορίων & το πρότυπο JTAG ή Προδιαγραφή JTAG καθιερώνεται. Η πολυπλοκότητα των ηλεκτρονικών αυξάνεται μέρα με τη μέρα, επομένως η προδιαγραφή JTAG έχει γίνει η αποδεκτή μορφή δοκιμής για τη δοκιμή πολύπλοκων και συμπαγών ηλεκτρονικών μονάδων. Αυτό το άρθρο εξετάζει μια επισκόπηση του α JTAG πρωτόκολλο – εργασία με εφαρμογές.

Τι είναι το JTAG;

Το όνομα που δίνεται στη θύρα πρόσβασης τυπικής δοκιμής IEEE 1149.1 καθώς και στην αρχιτεκτονική σάρωσης ορίων είναι γνωστό ως JTAG (Joint Test Action Group). Αυτή η αρχιτεκτονική σάρωσης ορίων χρησιμοποιείται κυρίως σε υπολογιστή επεξεργαστές γιατί ο πρώτος επεξεργαστής με JTAG κυκλοφόρησε από την Intel. Αυτό το πρότυπο IEEE ορίζει απλώς πώς ελέγχεται το κύκλωμα ενός υπολογιστή για να επιβεβαιωθεί εάν λειτουργεί σωστά μετά τη διαδικασία κατασκευής. Στις πλακέτες κυκλωμάτων, πραγματοποιούνται δοκιμές για τον έλεγχο των αρθρώσεων συγκόλλησης.

Το Joint Test Action Group παρέχει μια προβολή pins-out για τους δοκιμαστές με κάθε πληκτρολόγιο IC που βοηθά στον εντοπισμό τυχόν βλαβών σε μια πλακέτα κυκλώματος. Μόλις αυτό το πρωτόκολλο συνδεθεί με ένα τσιπ, αυτό μπορεί να συνδέσει έναν ανιχνευτή στο τσιπ επιτρέποντας σε έναν προγραμματιστή να ελέγχει το τσιπ καθώς και τις συνδέσεις του με άλλα τσιπ. Η διεπαφή με την ομάδα Joint Test Action μπορεί επίσης να χρησιμοποιηθεί από προγραμματιστές για την αντιγραφή του υλικολογισμικού σε μη πτητική μνήμη σε μια ηλεκτρονική συσκευή.

Διαμόρφωση/Pin Out

Η Ομάδα Δράσης Κοινής Δοκιμής περιλαμβάνει 20 ακίδες όπου η κάθε ακίδα και η λειτουργία της συζητούνται παρακάτω.

Pin1 (VTref): Αυτός είναι ο ακροδέκτης τάσης αναφοράς στόχου που χρησιμοποιείται για τη σύνδεση στο κύριο τροφοδοτικό του στόχου που κυμαίνεται από 1,5 έως 5,0 VDC.

Pin2 (Vsupply): Αυτή είναι η τάση τροφοδοσίας στόχου που χρησιμοποιείται για τη σύνδεση της κύριας παροχής τάσης του στόχου 1,5VDC – 5,0VDC.

Pin3 (nTRST): Αυτή είναι μια δοκιμαστική ακίδα επαναφοράς που χρησιμοποιείται για την επαναφορά του μηχανήματος κατάστασης του ελεγκτή TAP.

Καρφίτσες (4, 6, 8, 10, 12, 14, 16, 18 & 20): Αυτές είναι κοινές ακίδες GND.

Pin5 (TDI): Αυτά είναι τα δεδομένα δοκιμής στην καρφίτσα. Αυτά τα δεδομένα μεταφέρονται στη συσκευή προορισμού. Αυτή η καρφίτσα πρέπει να τραβηχτεί προς τα πάνω σε μια καθορισμένη κατάσταση στον πίνακα στόχο.

Pin7 (TMS): Αυτή είναι η ακίδα κατάστασης λειτουργίας δοκιμής που τραβιέται για να προσδιοριστεί η επόμενη κατάσταση της μηχανής κατάστασης του ελεγκτή TAP.

Pin9 (TCK): Αυτή είναι μια δοκιμαστική ακίδα ρολογιού που συγχρονίζει τις λειτουργίες της μηχανής εσωτερικής κατάστασης στον ελεγκτή TAP.

Pin11 (RTCK): Αυτό είναι το Input Return TCK pin που χρησιμοποιείται σε συσκευές που υποστηρίζουν προσαρμοστικό ρολόι.

Pin13 (TDO): Αυτή είναι η ακίδα Test Data Out, έτσι τα δεδομένα μετακινούνται από τη συσκευή-στόχο στο Flyswatter.

Pin15 (nSRST): Αυτή είναι η ακίδα επαναφοράς συστήματος στόχου που συνδέεται με το κύριο σήμα επαναφοράς του στόχου.

Pins 17 & 19 (NC): Αυτές δεν είναι συνδεδεμένες ακίδες.

JTAG Λειτουργεί

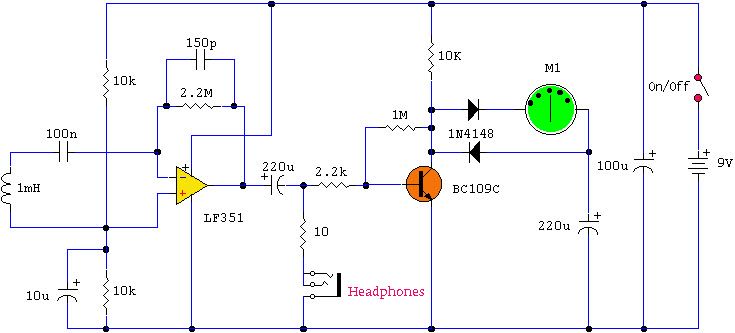

Η αρχική χρήση του JTAG είναι για δοκιμές ορίων. Εδώ, είναι μια απλή πλακέτα τυπωμένου κυκλώματος που περιλαμβάνει δύο IC όπως CPU και FPGA . Μια τυπική πλακέτα μπορεί να περιλαμβάνει πολλά IC. Γενικά, τα IC περιλαμβάνουν πολλές ακίδες που συνδέονται μαζί με πολλές συνδέσεις. Εδώ, στο παρακάτω διάγραμμα, φαίνονται μόνο τέσσερις συνδέσεις.

Έτσι, εάν σχεδιάσετε πολλές σανίδες όπου κάθε πλακέτα έχει χιλιάδες συνδέσεις. Σε αυτό, υπάρχουν κάποιες κακές σανίδες. Πρέπει λοιπόν να ελέγξουμε ποια πλακέτα λειτουργεί και ποια δεν λειτουργεί. Για αυτό, σχεδιάστηκε η Κοινή Ομάδα Δράσης Δοκιμών.

Αυτό το πρωτόκολλο μπορεί να χρησιμοποιήσει τις ακίδες ελέγχου όλων των τσιπ, αλλά στο παρακάτω διάγραμμα, η Ομάδα Δράσης Κοινής Δοκιμής πρόκειται να δημιουργήσει όλες τις ακίδες εξόδου της CPU & όλες τις ακίδες εισόδου του FPGA. Μετά από αυτό, μεταδίδοντας κάποια ποσότητα δεδομένων από τις ακίδες της CPU & διαβάζοντας τις τιμές των ακίδων από το FPGA, η JTAG δηλώνει ότι οι συνδέσεις της πλακέτας PCB είναι καλές.

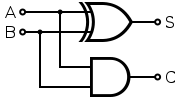

Στην πραγματικότητα, η Ομάδα Δράσης Κοινής Δοκιμής περιλαμβάνει τέσσερα λογικά σήματα TDI, TDO, TMS & TCK. Και αυτά τα σήματα πρέπει να συνδέονται με συγκεκριμένο τρόπο. Αρχικά, τα TMS & TCK συνδέονται παράλληλα με όλα τα IC της JTAG.

Μετά από αυτό, τόσο το TDI όσο και το TDO συνδέονται για να σχηματίσουν μια αλυσίδα. Όπως μπορείτε να παρατηρήσετε, κάθε IC συμβατό με JTAG περιλαμβάνει 4 ακίδες που χρησιμοποιούνται για το JTAG όπου οι 3 ακίδες είναι είσοδοι και η 4η ακίδα είναι η έξοδος. Η πέμπτη ακίδα όπως το TRST είναι προαιρετική. Συνήθως, οι ακίδες JTAG δεν κοινοποιούνται για άλλους σκοπούς.

Χρησιμοποιώντας την Ομάδα Δράσης Κοινής Δοκιμής, όλα τα IC χρησιμοποιούν δοκιμές ορίων που ο αρχικός λόγος δημιουργείται από την JTAG. Προς το παρόν, η χρήση αυτού του πρωτοκόλλου έχει επεκταθεί για να επιτρέψει διάφορα πράγματα, όπως η διαμόρφωση των FPGA και στη συνέχεια το JTAG χρησιμοποιείται στον πυρήνα FPGA για σκοπούς εντοπισμού σφαλμάτων.

Αρχιτεκτονική JTAG

Η αρχιτεκτονική JTAG φαίνεται παρακάτω. Σε αυτήν την αρχιτεκτονική, όλα τα σήματα μεταξύ της λογικής πυρήνα της συσκευής και των ακίδων διακόπτονται μέσω μιας σειριακής διαδρομής σάρωσης που ονομάζεται BSR ή Boundary Scan Register. Αυτό το BSR περιλαμβάνει διάφορα «κελιά» σάρωσης ορίων. Γενικά, αυτά τα κελιά οριακής σάρωσης δεν είναι ορατά, αλλά μπορούν να χρησιμοποιηθούν για τον ορισμό ή την ανάγνωση τιμών στη λειτουργία δοκιμής από τις ακίδες της συσκευής.

Η διεπαφή JTAG που ονομάζεται TAP ή Test Access Port χρησιμοποιεί διαφορετικά σήματα για την υποστήριξη της λειτουργίας σάρωσης ορίων όπως TCK, TMS, TDI, TDO και TRST.

- Το σήμα TCK ή Test Clock απλώς συγχρονίζει τις εσωτερικές λειτουργίες μιας κατάστασης μηχανής.

- Το σήμα TMS ή Test Mode Select λαμβάνεται δειγματοληπτικά στην αύξουσα άκρη ενός σήματος ρολογιού δοκιμής για να αποφασιστεί η επόμενη κατάσταση.

- Το σήμα TDI ή Test Data In υποδηλώνει τα μετατοπισμένα δεδομένα στη δοκιμαστική συσκευή, διαφορετικά η λογική προγραμματισμού. Μόλις η μηχανή εσωτερικής κατάστασης βρίσκεται στη σωστή κατάσταση, τότε γίνεται δειγματοληψία στην αυξανόμενη άκρη του TCK.

- Το σήμα TDO ή Test Data Out υποδηλώνει τα μετατοπισμένα δεδομένα της δοκιμαστικής συσκευής, αλλιώς λογική προγραμματισμού. Μόλις η μηχανή εσωτερικής κατάστασης είναι στη σωστή κατάσταση, τότε ισχύει στην φθίνουσα άκρη του TCK

- Το TRST ή το Test Reset είναι μια προαιρετική καρφίτσα που χρησιμοποιείται για την επαναφορά του μηχανήματος κατάστασης του ελεγκτή TAP.

Ελεγκτής TAP

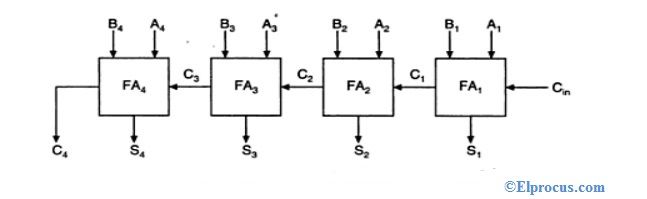

Το δοκιμαστικό σημείο πρόσβασης στην αρχιτεκτονική του JTAG αποτελείται από έναν ελεγκτή TAP, έναν καταχωρητή εντολών και καταχωρητές δεδομένων δοκιμής. Αυτός ο ελεγκτής περιλαμβάνει το μηχάνημα κατάστασης δοκιμής που είναι υπεύθυνο για την ανάγνωση των σημάτων TMS & TCK. Εδώ, η ακίδα δεδομένων i/p χρησιμοποιείται απλώς για τη φόρτωση δεδομένων στα οριακά κελιά μεταξύ του πυρήνα IC και των φυσικών ακροδεκτών, και επίσης για τη φόρτωση δεδομένων σε έναν από τους καταχωρητές δεδομένων ή στον καταχωρητή εντολών. Η καρφίτσα δεδομένων o/p χρησιμοποιείται για την ανάγνωση δεδομένων είτε από τους καταχωρητές είτε από τα οριακά κελιά.

Το μηχάνημα κατάστασης του ελεγκτή TAP ελέγχεται από το TMS και χρονομετρείται από το TCK. Το μηχάνημα κατάστασης χρησιμοποιεί δύο μονοπάτια για να υποδηλώσει δύο διαφορετικούς τρόπους λειτουργίας, όπως λειτουργία εντολών και λειτουργία δεδομένων.

Μητρώα

Υπάρχουν δύο είδη καταχωρητών που είναι διαθέσιμα στη σάρωση ορίων. Κάθε συμβατή συσκευή περιλαμβάνει τουλάχιστον δύο καταχωρητές δεδομένων και έναν καταχωρητή εντολών.

Μητρώο Οδηγιών

Ο καταχωρητής εντολών χρησιμοποιείται για τη διατήρηση της τρέχουσας εντολής. Έτσι, τα δεδομένα του χρησιμοποιούνται από τον ελεγκτή TAP για να αποφασίσει τι θα εκτελέσει με τα σήματα που λαμβάνονται. Τις περισσότερες φορές, τα δεδομένα του καταχωρητή εντολών θα περιγράφουν σε ποιον από τους καταχωρητές δεδομένων πρέπει να περάσουν τα σήματα.

Μητρώα Δεδομένων

Οι καταχωρητές δεδομένων είναι διαθέσιμοι σε τρεις τύπους, τον καταχωρητή BSR (Boundary Scan Register), τον BYPASS & τον καταχωρητή ID CODES. Επίσης, μπορεί να υπάρχουν και άλλα μητρώα δεδομένων, ωστόσο δεν είναι απαραίτητα ως στοιχείο του προτύπου JTAG.

Καταχωρητής σάρωσης ορίων (BSR)

Το BSR είναι ο κύριος καταχωρητής δεδομένων δοκιμής που χρησιμοποιείται για τη μετατόπιση δεδομένων από και προς τις ακίδες εισόδου/εξόδου της συσκευής.

ΠΑΡΑΚΑΜΨΗ

Το Bypass είναι ένας καταχωρητής ενός bit που χρησιμοποιείται για τη μετάδοση δεδομένων από το TDI – TDO. Έτσι επιτρέπει τον έλεγχο πρόσθετων συσκευών εντός ενός κυκλώματος με ελάχιστη επιβάρυνση.

ΚΩΔΙΚΟΙ ΤΑΥΤΟΤΗΤΑΣ

Αυτός ο τύπος μητρώου δεδομένων περιλαμβάνει τον κωδικό ID καθώς και τον αριθμό αναθεώρησης για τη συσκευή. Επομένως, αυτά τα δεδομένα επιτρέπουν στη συσκευή να συνδεθεί στο αρχείο BSDL (Γλώσσα περιγραφής σάρωσης ορίων). Αυτό το αρχείο περιλάμβανε τις λεπτομέρειες ρύθμισης παραμέτρων σάρωσης ορίων για τη συσκευή.

Η λειτουργία του JTAG είναι, αρχικά, ο τρόπος λειτουργίας εντολής που επιλέγεται όπου μία από τις καταστάσεις σε αυτόν τον τρόπο λειτουργίας «διαδρομή» αφήνει τον χειριστή να ρολόι μέσα σε μια εντολή από το TDI. Μετά από αυτό., η κρατική μηχανή αναπτύσσεται μέχρι να αναδιαταχθεί. Το επόμενο βήμα για τις περισσότερες οδηγίες είναι να επιλέξετε τη λειτουργία δεδομένων. Έτσι, σε αυτή τη λειτουργία, τα δεδομένα φορτώνονται μέσω TDI για ανάγνωση από TDO. Για το TDI & TDO, οι διαδρομές δεδομένων θα διευθετηθούν σύμφωνα με την εντολή που έχει χρονομετρηθεί. Μόλις ολοκληρωθεί η λειτουργία ανάγνωσης/εγγραφής, η μηχανή καταστάσεων αναπτύσσεται ξανά στην κατάσταση επαναφοράς.

Διαφορά μεταξύ JTAG και UART

Η διαφορά μεταξύ JTAG και UART περιλαμβάνει τα ακόλουθα.

| JTAG |

UART |

| Ο όρος 'JTAG' σημαίνει Κοινή Ομάδα Δράσης Δοκιμών. | Ο όρος ' UART ” σημαίνει Universal Asynchronous Receiver/Transmitter. |

| Είναι μια σύγχρονη διεπαφή που χρησιμοποιεί ενσωματωμένο υλικό για τον προγραμματισμό του φλας . | Το UART είναι μια ασύγχρονη διεπαφή που χρησιμοποιεί ένα bootloader που εκτελείται στη μνήμη. |

| Είναι ένα σύνολο δοκιμαστικών θυρών που χρησιμοποιούνται για εντοπισμό σφαλμάτων, αλλά μπορούν επίσης να χρησιμοποιηθούν για τον προγραμματισμό υλικολογισμικού (κάτι που συνήθως γίνεται).

|

Το UART είναι ένας τύπος τσιπ που ελέγχει τις επικοινωνίες από και προς μια συσκευή, όπως μικροελεγκτή, ROM, RAM, κ.λπ. Τις περισσότερες φορές, είναι μια σειριακή σύνδεση που μας επιτρέπει να επικοινωνούμε με μια συσκευή. |

| Διατίθενται σε τέσσερις τύπους TDI, TDO, TCK, TMS & TRST. | Αυτά είναι διαθέσιμα σε δύο τύπους dumb UART & FIFO UART. |

| Το Joint Test Action Group είναι πρωτόκολλο σειριακού προγραμματισμού ή πρόσβασης δεδομένων που χρησιμοποιείται στη διασύνδεση μικροελεγκτών και σχετικών συσκευών. | Το UART είναι ένα είδος τσιπ, διαφορετικά το υποσυστατικό του μικροελεγκτή που χρησιμοποιείται για την παροχή του υλικού για τη δημιουργία μιας ασύγχρονης σειριακής ροής όπως το RS-232/RS-485. |

| Τα στοιχεία JTAG είναι επεξεργαστές, FPGA, CPLD , και τα λοιπά. | Τα στοιχεία UART είναι γεννήτρια CLK, καταχωρητές μετατόπισης I/O, buffer μετάδοσης ή λήψης, buffer διαύλου δεδομένων συστήματος, λογική ελέγχου ανάγνωσης ή εγγραφής κ.λπ. |

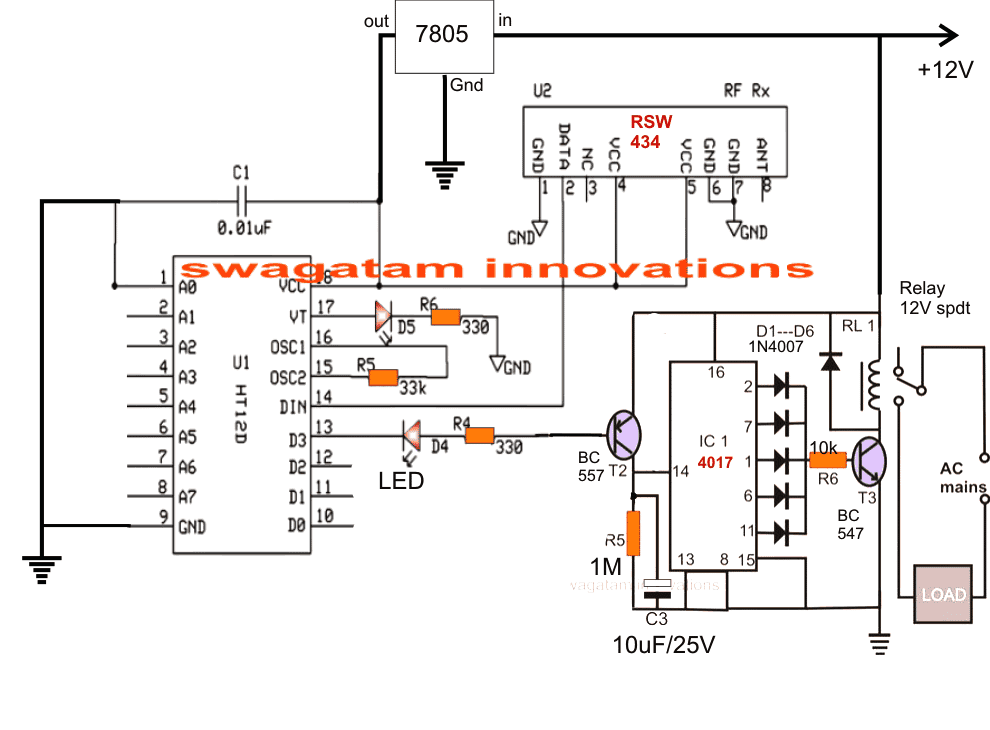

Αναλυτής πρωτοκόλλου JTAG

Ο αναλυτής πρωτοκόλλου JTAG, όπως ο PGY-JTAG-EX-PD, είναι ένα είδος αναλυτή πρωτοκόλλου που περιλαμβάνει ορισμένες δυνατότητες για την καταγραφή και τον εντοπισμό σφαλμάτων επικοινωνίας μεταξύ κεντρικού υπολογιστή και σχεδίασης υπό δοκιμή. Αυτός ο τύπος αναλυτή είναι το κορυφαίο όργανο που επιτρέπει στους μηχανικούς δοκιμής και σχεδίασης να δοκιμάζουν τα συγκεκριμένα σχέδια του JTAG για τις προδιαγραφές του μέσω της διευθέτησης του PGY-JTAG-EX-PD όπως Master ή Slave για τη δημιουργία κίνησης JTAG και την αποκωδικοποίηση των πακέτων αποκωδικοποίησης του Πρωτόκολλο Joint Test Action Group.

Χαρακτηριστικά

Τα χαρακτηριστικά του αναλυτή πρωτοκόλλου JTAG περιλαμβάνουν τα ακόλουθα.

- Υποστηρίζει έως και 25MH συχνοτήτων JTAG.

- Παράγει κίνηση JTAG και αποκωδικοποίηση πρωτοκόλλου για το Bus ταυτόχρονα.

- Διαθέτει JTAG Master Capability.

- Μεταβλητές ταχύτητες δεδομένων JTAG & κύκλος λειτουργίας.

- Καθυστερήσεις TDI & TCK που καθορίζονται από το χρήστη.

- Διασύνδεση κεντρικού υπολογιστή USB 2.0 ή 3.0.

- Ανάλυση σφαλμάτων μέσα στην αποκωδικοποίηση πρωτοκόλλου

- Διάγραμμα χρονισμού διαύλου αποκωδικοποιημένο με πρωτόκολλο.

- Συνεχής ροή δεδομένων πρωτοκόλλου στον κεντρικό υπολογιστή για παροχή μεγάλου buffer.

- Λίστα δραστηριοτήτων πρωτοκόλλου.

- Σε διάφορες ταχύτητες, μπορεί να γραφτεί ένα σενάριο άσκησης για το συνδυασμό δημιουργίας πολλαπλών πλαισίων δεδομένων.

Διάγραμμα χρονισμού

ο διάγραμμα χρονισμού του JTAG το πρωτόκολλο φαίνεται παρακάτω. Στο παρακάτω διάγραμμα, η ακίδα TDO παραμένει εντός της συνθήκης υψηλής σύνθετης αντίστασης εκτός από την κατάσταση του ελεγκτή shift-IR/shift-DR.

Στις συνθήκες του ελεγκτή shift-IR & Shift-DR, η ακίδα TDO ενημερώνεται στην φθίνουσα άκρη του TCK μέσω του Target και γίνεται δειγματοληψία στην αυξανόμενη άκρη του TCK μέσω του Host.

Απλώς γίνεται δειγματοληψία και των δύο καρφίδων TDI και TMS στην αυξανόμενη άκρη του TCK μέσω του Target. Ενημερώθηκε στην φθίνουσα άκρη διαφορετικά TCK μέσω του κεντρικού υπολογιστή.

Εφαρμογές

ο Εφαρμογές JTAG περιλαμβάνουν τα ακόλουθα.

- Το Joint Test Action Group χρησιμοποιείται συχνά στους επεξεργαστές για την παροχή του δικαιώματος εισόδου στις λειτουργίες εξομοίωσης ή εντοπισμού σφαλμάτων.

- Όλα τα CPLD & FPGA το χρησιμοποιούν ως διεπαφή για να παρέχουν πρόσβαση στις λειτουργίες προγραμματισμού τους.

- Χρησιμοποιείται για δοκιμές PCB χωρίς φυσική πρόσβαση

- Χρησιμοποιείται για δοκιμές κατασκευής σε επίπεδο σανίδας.

Επομένως, πρόκειται για όλα μια επισκόπηση του JTAG – διαμόρφωση pin, εργασία με εφαρμογές. Το βιομηχανικό πρότυπο JTAG χρησιμοποιείται για επαλήθευση σχεδιασμού καθώς και για δοκιμή PCB μετά την κατασκευή. Εδώ είναι μια ερώτηση για εσάς, το JTAG σημαίνει;