Το RISC V είναι μια αρχιτεκτονική συνόλων εντολών που αναπτύχθηκε από το Πανεπιστήμιο της Καλιφόρνια στο Μπέρκλεϋ. Η ιδέα του RISC υποκινήθηκε από την αλήθεια ότι οι περισσότερες από τις οδηγίες του επεξεργαστή δεν χρησιμοποιήθηκαν από τα περισσότερα προγράμματα υπολογιστών. Έτσι, χρησιμοποιήθηκε περιττή λογική αποκωδικοποίησης στα σχέδια του επεξεργαστές , καταναλώνοντας περισσότερη ενέργεια καθώς και περιοχή. Για να συντομεύσετε το σύνολο εντολών και να επενδύσετε περισσότερο στους πόρους του μητρώου, το Επεξεργαστής RISC V εφαρμόστηκε.

Αυτή η τεχνολογία έγινε αντιληπτή από πολλούς τεχνολογικούς γίγαντες και νεοφυείς επιχειρήσεις επειδή είναι εντελώς ανοιχτού κώδικα και δωρεάν. Οι περισσότεροι τύποι επεξεργαστών διατίθενται με άδεια χρήσης, ωστόσο με αυτόν τον τύπο επεξεργαστή. Ο καθένας μπορεί να κάνει τα νέα του σχέδια επεξεργαστή. Έτσι, αυτό το άρθρο εξετάζει μια επισκόπηση ενός επεξεργαστή RISC V - που λειτουργεί και οι εφαρμογές του.

Τι είναι ο επεξεργαστής RISC V;

Στον επεξεργαστή RISC V, ο όρος RISC σημαίνει 'υπολογιστής μειωμένου συνόλου εντολών' που εκτελεί λίγες εντολές υπολογιστή ενώ το 'V' σημαίνει την 5η γενιά. Είναι ένα ISA υλικού ανοιχτού κώδικα (αρχιτεκτονική συνόλου εντολών) που βασίζεται στην καθιερωμένη αρχή του ΚΙΝΔΥΝΟΣ .

Σε σύγκριση με άλλα σχέδια ISA, αυτό το ISA διατίθεται με άδεια ανοιχτού κώδικα. Έτσι, ένας αριθμός κατασκευαστικών εταιρειών ανακοίνωσαν και παρείχαν επίσης υλικό RISC-V, με λειτουργικά συστήματα ανοιχτού κώδικα.

Αυτή είναι μια νέα αρχιτεκτονική και διατίθεται σε ανοιχτές, μη περιοριστικές & δωρεάν άδειες χρήσης. Αυτός ο επεξεργαστής έχει εκτεταμένη υποστήριξη από βιομηχανίες κατασκευής τσιπ και συσκευών. Έτσι, έχει σχεδιαστεί κυρίως για να είναι ελεύθερα επεκτάσιμο και προσαρμόσιμο για χρήση σε πολλές εφαρμογές.

RISC V Ιστορία

Το RISC επινοήθηκε από τον καθηγητή David Patterson γύρω στο 1980 στο Πανεπιστήμιο της Καλιφόρνια στο Μπέρκλεϋ. Ο καθηγητής David με τον καθηγητή John Hennessy υπέβαλαν τις προσπάθειές τους σε δύο βιβλία και συγκεκριμένα «Οργάνωση και Σχεδιασμός Υπολογιστών» και «Αρχιτεκτονική Υπολογιστών στο Πανεπιστήμιο του Στάνφορντ». Έτσι, έλαβαν το ACM A.M. Βραβείο Turing το έτος 2017.

Από το έτος 1980 έως το έτος 2010, ξεκίνησε η έρευνα ανάπτυξης πέμπτης γενιάς RISC και τελικά προσδιορίστηκε ως RISC-V που προφέρεται ως κίνδυνος πέντε.

RISC V Architecture & Working

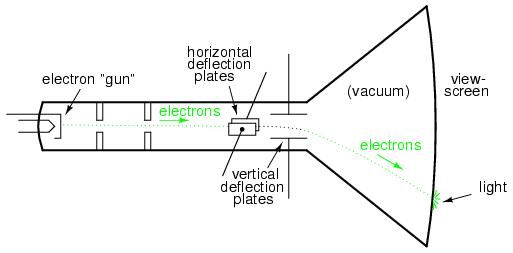

Η αρχιτεκτονική RV12 RISC V φαίνεται παρακάτω. Το RV12 είναι εξαιρετικά διαμορφώσιμο με επεξεργαστή RISC συμβατό με μονοπύρηνο RV32I και RV64I που χρησιμοποιείται σε ενσωματωμένα πεδία. Το RV12 προέρχεται επίσης από μια οικογένεια CPU 32 ή 64 bit, ανάλογα με το βιομηχανικό πρότυπο σύνολο εντολών RISC-V.

Το RV12 απλώς εκτελεί μια αρχιτεκτονική του Χάρβαρντ για ταυτόχρονη πρόσβαση στις οδηγίες καθώς και στη μνήμη δεδομένων. Περιλαμβάνει επίσης μια διοχέτευση 6 σταδίων που βοηθά στη βελτιστοποίηση των επικαλύψεων μεταξύ της εκτέλεσης καθώς και των προσβάσεων στη μνήμη για τη βελτίωση της απόδοσης. Αυτή η αρχιτεκτονική περιλαμβάνει κυρίως Branch Prediction, Data Cache, Debug Unit, Instruction Cache και προαιρετικές Multiplier ή Divider Units.

Τα κύρια χαρακτηριστικά του RV12 RISC V περιλαμβάνουν τα ακόλουθα.

- Είναι ένα πρότυπο σετ οδηγιών βιομηχανίας.

- Παραμετροποιείται με δεδομένα 32 ή 64 bit.

- Έχει ακριβείς και γρήγορες διακοπές.

- Οι προσαρμοσμένες οδηγίες επιτρέπουν την προσθήκη ιδιόκτητων επιταχυντών υλικού.

- Εκτέλεση μονού κύκλου.

- Σωλήνας έξι σταδίων με βελτιστοποίηση διπλωμένο.

- Υποστήριξη με προστασία μνήμης.

- Προαιρετικές ή Παραμετροποιημένες κρυφές μνήμες.

- Εξαιρετικά παραμετροποιημένο.

- Οι χρήστες μπορούν να επιλέξουν Μονάδα Πρόβλεψης Δεδομένων 32/64-bit.

- Οι χρήστες μπορούν να επιλέξουν κρυφές μνήμες εντολών/δεδομένων.

- Δομή, μέγεθος και αρχιτεκτονική της κρυφής μνήμης με δυνατότητα επιλογής από τον χρήστη.

- Υποστήριξη διαιρέτη ή πολλαπλασιαστή υλικού με καθυστέρηση που καθορίζεται από το χρήστη.

- Η αρχιτεκτονική του λεωφορείου είναι ευέλικτη και υποστηρίζει Wishbone & AHB.

- Αυτός ο σχεδιασμός βελτιστοποιεί την ισχύ και το μέγεθος.

- Ο σχεδιασμός είναι πλήρως παραμετροποιημένος που παρέχει αντισταθμίσεις απόδοσης ή ισχύος.

- Περιφραγμένη σχεδίαση CLK για μείωση ισχύος.

- Υποστήριξη λογισμικού κατά Industry standard.

- Αρχιτεκτονικός προσομοιωτής.

- Το Eclipse IDE χρησιμοποιείται για Linux/ Windows.

Ο αγωγός εκτέλεσης RISC V

Περιλαμβάνει πέντε στάδια όπως IF (ανάκτηση εντολών), ID (αποκωδικοποίηση εντολών), EX (εκτέλεση), MEM (πρόσβαση στη μνήμη) και WB (επαναγραφή μητρώου).

Λήψη οδηγιών

Στο στάδιο Instruction Fetch ή IF, διαβάζεται μια μεμονωμένη εντολή από τον μετρητή προγράμματος (PC) και τη μνήμη εντολών που ενημερώνεται στην επόμενη εντολή.

Οδηγίες Προ-αποκωδικοποίηση

Μόλις επιτραπεί η υποστήριξη RVC, τότε το στάδιο Instruction Pre-Decode θα αποκωδικοποιήσει μια συμπιεσμένη εντολή 16-bit σε μια εγγενή εντολή 32-bit.

Οδηγίες Αποκωδικοποίηση

Στο στάδιο Αποκωδικοποίηση εντολών (ID), επιτρέπεται το Αρχείο Καταχώρησης και αποφασίζονται οι έλεγχοι παράκαμψης.

Εκτέλεση

Στο στάδιο Εκτέλεση, το αποτέλεσμα υπολογίζεται για μια εντολή ALU, DIV, MUL, η μνήμη που επιτρέπεται για μια εντολή αποθήκευσης ή φόρτωσης και οι διακλαδώσεις και τα άλματα μετρώνται σε σχέση με τα αναμενόμενα αποτελέσματά τους.

Μνήμη

Σε αυτό το στάδιο της μνήμης, η πρόσβαση στη μνήμη γίνεται μέσω του αγωγού. Η συμπερίληψη αυτής της φάσης διασφαλίζει την υψηλή απόδοση του αγωγού.

Γράψε πίσω

Σε αυτό το στάδιο, το αποτέλεσμα του σταδίου εκτέλεσης εγγράφεται στο αρχείο μητρώου.

Branch Predictor

Αυτός ο επεξεργαστής περιλαμβάνει μια μονάδα πρόβλεψης διακλάδωσης ή BPU που χρησιμοποιείται για την αποθήκευση προηγούμενων δεδομένων για να καθοδηγήσει τον επεξεργαστή RISC V να αποφασίσει εάν μια συγκεκριμένη διακλάδωση θα ληφθεί ή όχι-. Αυτά τα δεδομένα πρόβλεψης απλώς ενημερώνονται μόλις εκτελεστεί ο κλάδος.

Αυτή η μονάδα περιλαμβάνει διαφορετικές παραμέτρους που καθορίζουν τη συμπεριφορά της. Για παράδειγμα, το HAS_BPU χρησιμοποιείται για να προσδιορίσει εάν ένας κλάδος προβλέπει ότι υπάρχει μια μονάδα, το BPU_GLOBAL_BITS θα καθορίσει πόσα προηγούμενα bit πρέπει να χρησιμοποιηθούν και το BPU_LOCAL_BITS θα καθορίσει πόσα από τα LSB του μετρητή προγράμματος θα πρέπει να χρησιμοποιηθούν. Ο συνδυασμός BPU_LOCAL_BITS & BPU_GLOBAL_BITS θα δημιουργήσει ένα διάνυσμα που χρησιμοποιείται κυρίως για την αντιμετώπιση του Πίνακα Πρόβλεψης Διακλάδωσης.

Προσωρινή μνήμη δεδομένων

Αυτό χρησιμοποιείται κυρίως για την επιτάχυνση της πρόσβασης στη μνήμη δεδομένων με την προσωρινή αποθήκευση θέσεων της μνήμης που προσπελάστηκαν πρόσφατα. Αυτό είναι ικανό να χειρίζεται προσβάσεις μισής λέξης, byte και λέξης όταν XLEN = 32, εάν βρίσκονται στα δικά τους όρια. Είναι επίσης ικανό να χειρίζεται προσβάσεις μισής λέξης, byte, λέξης και διπλής λέξης όταν XLEN=64, εάν βρίσκονται στα δικά τους όρια.

Κατά τη διάρκεια μιας απώλειας προσωρινής μνήμης, ένα ολόκληρο μπλοκ μπορεί να γραφτεί πίσω στη μνήμη, οπότε εάν είναι απαραίτητο, ένα νέο μπλοκ μπορεί να φορτωθεί στη μνήμη cache. Η προσωρινή μνήμη δεδομένων απενεργοποιείται ορίζοντας το DCACHE_SIZE σε μηδέν. Μετά από αυτό, οι θέσεις μνήμης είναι προσβάσιμες απευθείας μέσω του Διεπαφή δεδομένων .

Προσωρινή μνήμη εντολών

Αυτό χρησιμοποιείται κυρίως για την επιτάχυνση της ανάκτησης εντολών με την προσωρινή αποθήκευση εντολών που ανακτήθηκαν πρόσφατα. Αυτή η κρυφή μνήμη χρησιμοποιείται για την ανάκτηση ενός δέματος για κάθε κύκλο σε οποιοδήποτε όριο 16-bit αλλά όχι σε ένα όριο μπλοκ. Κατά τη διάρκεια μιας απώλειας προσωρινής μνήμης, ένα ολόκληρο μπλοκ μπορεί να φορτωθεί από τη μνήμη εντολών. Η διαμόρφωση αυτής της κρυφής μνήμης μπορεί να γίνει με βάση τις ανάγκες του χρήστη. Το μέγεθος της κρυφής μνήμης, ο αλγόριθμος αντικατάστασης και το μήκος του μπλοκ μπορούν να διαμορφωθούν.

Ο κύκλος εντολών θα απενεργοποιηθεί ορίζοντας το ICACHE_SIZE στο μηδέν. Μετά από αυτό, τα δέματα λαμβάνονται απευθείας από τη μνήμη μέσω του Διεπαφή οδηγιών.

Μονάδα εντοπισμού σφαλμάτων

Η μονάδα εντοπισμού σφαλμάτων θα επιτρέψει στο περιβάλλον εντοπισμού σφαλμάτων να σταματήσει και να εξετάσει τη CPU. Τα κύρια χαρακτηριστικά αυτού είναι Branch Tracing, Single Step Tracing έως 8- Hardware Breakpoints.

Αρχείο εγγραφής

Αυτό έχει σχεδιαστεί με 32 θέσεις καταχωρήσεων από το X0 έως το X31 όπου το X9 Register είναι πάντα μηδέν. Το Αρχείο Εγγραφής περιλαμβάνει 1 θύρα εγγραφής και 2 θύρες ανάγνωσης.

Διαμόρφωση διεπαφής

Αυτή είναι μια εξωτερική διεπαφή όπου αυτός ο επεξεργαστής υποστηρίζει διαφορετικές διεπαφές εξωτερικού διαύλου.

Πώς λειτουργεί το RISC V;

Το RISC-V είναι μια αρχιτεκτονική συνόλου εντολών που βασίζεται στις αρχές του RISC (υπολογιστής μειωμένου συνόλου εντολών). Αυτός ο επεξεργαστής είναι πολύ μοναδικός και επίσης επαναστατικός καθώς είναι ένα δωρεάν, κοινό και ανοιχτού κώδικα ISA όπου μπορεί να αναπτυχθεί υλικό, να μεταφερθεί το λογισμικό και να σχεδιαστούν επεξεργαστές για να το υποστηρίζουν.

Διαφορά Α/Β RISC V έναντι MIPS

Η διαφορά μεταξύ RISC V και MIPS περιλαμβάνει τα ακόλουθα.

|

RISC V |

MIPS |

| Ο όρος RISC V σημαίνει Υπολογιστής μειωμένου συνόλου εντολών όπου το 'V' είναι η πέμπτη γενιά. | Ο όρος 'MIPS' σημαίνει 'Εκατομμύρια οδηγίες ανά δευτερόλεπτο'. |

| Το RISC-V απλώς επιτρέπει στους κατασκευαστές μικρότερων συσκευών να σχεδιάζουν υλικό χωρίς να πληρώνουν. | Το MIPS επιτρέπει στον κατασκευαστή να μετρήσει την ταχύτητα του επεξεργαστή πληρώνοντας επειδή δεν είναι δωρεάν. |

| Το MIPS είναι αποτελεσματικά νεκρό. | Το RISC-V δεν είναι αποτελεσματικά νεκρό. |

| Αυτός ο επεξεργαστής παρέχει οδηγίες διακλάδωσης για σύγκριση δύο καταχωρητών. | Το MIPS εξαρτάται από μια εντολή σύγκρισης που εντοπίζει έναν καταχωρητή στο 1 ή στο 0 με βάση το αν η αντίθεση είναι αληθής. |

| Το σχήμα κωδικοποίησης ISA είναι σταθερό και μεταβλητό στο RISC V. | Το σχήμα κωδικοποίησης ISA είναι σταθερό στο MIPS |

| Το μέγεθος του συνόλου εντολών είναι 16-bit ή 32-bit ή 64-bit ή 128-bit. | Το μέγεθος του συνόλου εντολών είναι 32-bit ή 64-bit. |

| Διαθέτει 32 μητρώα γενικής χρήσης και κινητής υποδιαστολής | Διαθέτει 31 μητρώα γενικής χρήσης και κινητής υποδιαστολής. |

| Διαθέτει λειτουργίες κινητής υποδιαστολής 26 μονής & διπλής ακρίβειας. | Διαθέτει λειτουργίες κινητής υποδιαστολής 15 μονής & διπλής ακρίβειας. |

Διαφορά Α/Β RISC Vs ARM

Η διαφορά μεταξύ RISC Vs ARM περιλαμβάνει τα ακόλουθα.

|

RISC V |

ΜΠΡΑΤΣΟ |

| Το RISC-V είναι ανοιχτού κώδικα, επομένως δεν απαιτεί καμία άδεια. | Το ARM είναι κλειστή πηγή, επομένως χρειάζεται άδεια. |

| Είναι μια νέα πλατφόρμα επεξεργαστή, επομένως υπάρχει πολύ μικρή υποστήριξη για περιβάλλοντα λογισμικού και προγραμματισμού. | Η ARM διαθέτει μια πολύ μεγάλη διαδικτυακή κοινότητα, η οποία υποστηρίζει βιβλιοθήκες και δομές για να βοηθήσει τους σχεδιαστές-στόχους σε διάφορες πλατφόρμες όπως μικροεπεξεργαστές, μικροελεγκτές και επίσης διακομιστές. |

| Τα τσιπ που βασίζονται σε RISC V χρησιμοποιούν ισχύ 1 watt. | Τα τσιπ που βασίζονται σε ARM χρησιμοποιούν ισχύ κάτω από 4 watt. |

| Διαθέτει σταθερό & μεταβλητό σύστημα κωδικοποίησης ISA. | Διαθέτει σταθερό σύστημα κωδικοποίησης ISA. |

| Το μέγεθος του συνόλου εντολών RISC V κυμαίνεται από 16-bit έως 128-bit. | Το μέγεθος εντολών του κυμαίνεται από 16-bit έως 64-bit. |

| Περιλαμβάνει 32 μητρώα γενικής χρήσης και κινητής υποδιαστολής. | Περιλαμβάνει 31 μητρώα γενικής χρήσης και κινητής υποδιαστολής. |

| Διαθέτει 26 λειτουργίες κινητής υποδιαστολής ακριβείας. | Διαθέτει 33 λειτουργίες κινητής υποδιαστολής ακριβείας. |

| Διαθέτει λειτουργίες κινητής υποδιαστολής 26 διπλής ακρίβειας. | Διαθέτει λειτουργίες κινητής υποδιαστολής 29 διπλής ακρίβειας. |

Κωδικός RISC V Verilog

Ο κωδικός verilog της μνήμης εντολών για το RISC φαίνεται παρακάτω.

// Κωδικός Verilog για τον επεξεργαστή RISC

// Κωδικός Verilog για Μνήμη Οδηγιών

ενότητα Instruction_Memory(

input[15:0] pc,

εντολή εξόδου[15:0]

)

reg [`col – 1:0] μνήμη [`row_i – 1:0];

καλώδιο [3 : 0] rom_addr = pc[4 : 1];

αρχικός

να αρχίσει

$readmemb(“./test/test.prog', μνήμη,0,14);

τέλος

assign instruction = memory[rom_addr];

endmodule

Κωδικός Verilog για τον επεξεργαστή RISC V 16-bit:

ενότητα Risc_16_bit(

εισαγωγή clk

)

wire jump,bne,beq,mem_read,mem_write,alu_src,reg_dst,mem_to_reg,reg_write;

wire[1:0] alu_op;

καλώδιο [3:0] opcode;

// Διαδρομή δεδομένων

Datapath_Unit DU

(

.clk(clk),

.άλμα (άλμα),

.frog(βάτραχος),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.reg_write(reg_write),

.bne(bne),

.alu_op(alu_op),

.opcode(opcode)

)

// μονάδα ελέγχου

Έλεγχος_Έλεγχος μονάδας

(

.opcode(opcode),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.alu_op(alu_op),

.άλμα (άλμα),

.bne(bne),

.frog(βάτραχος),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_write(reg_write)

)

endmodule

Σετ οδηγιών

Τα σύνολα εντολών RISC V συζητούνται παρακάτω.

Αριθμητικές Πράξεις

Οι αριθμητικές πράξεις RISC V παρατίθενται παρακάτω.

| Μνημονικός | Τύπος | Εντολή | Περιγραφή |

| ΠΡΟΣΘΗΚΗ rd, rs1, rs2 |

R |

Προσθήκη | rdß rs1 + rs2 |

| SUB rd, rs1, rs2 |

R |

Αφαιρώ | rdß rs1 – rs2 |

| ADDI rd, rs1, imm12 |

Εγώ |

Προσθέστε αμέσως | rdß rs1 + imm12 |

| SLT rd, rs1, rs2 |

R |

Ορίστε λιγότερο από | rdß rs1 -< rs2 |

| SLTI rd, rs1, imm12 |

Εγώ |

Ρυθμίστε λιγότερο από άμεσο | rdß rs1 -< imm12 |

| SLTU rd, rs1, rs2 |

R |

Ορίστε λιγότερο από ανυπόγραφο | rdß rs1 -< rs2 |

| SLTIU rd, rs1, imm12 |

Εγώ |

Ορισμός λιγότερο από άμεσο ανυπόγραφο | rdß rs1 -< imm12 |

| LUI rd, imm20 |

ΣΕ |

Φόρτωση επάνω αμέσως | rdß imm20<<12 |

| AUIP rd, imm20 |

ΣΕ |

Προσθέστε το επάνω άμεσο στον υπολογιστή | rdß PC+imm20<<12 |

Λογικές Λειτουργίες

Οι λογικές πράξεις RISC V παρατίθενται παρακάτω.

| Μνημονικός | Τύπος | Εντολή | Περιγραφή |

| ΚΑΙ rd, rs1, rs2 |

R |

ΚΑΙ | rdß rs1 & rs2 |

| Ή rd, rs1, rs2 |

R |

Ή | rdß rs1 | rs2 |

| XOR rd, rs1, rs2 |

R |

ΕΛΕΥΘΕΡΟΣ | rdß rs1 ^ rs2 |

| ANDI rd, rs1, imm12 |

Εγώ |

ΚΑΙ άμεσο | rdß rs1 & imm2 |

| ORI rd, rs1, imm12 |

Εγώ |

Ή Άμεσα | rdß rs1 | imm12 |

| OXRI rd, rs1, imm12 |

Εγώ |

XOR άμεσα | rdß rs1 ^ rs2 |

| SLL rd, rs1, rs2 |

R |

Λογική μετατόπιση αριστερά | rdß rs1 << rs2 |

| SRL rd, rs1, rs2 |

R |

Αλλαγή λογικής δεξιά | rdß rs1 >> rs2 |

| RAS rd, rs1, rs2 |

R |

Μετατόπιση αριθμητικής προς τα δεξιά | rdß rs1 >> rs2 |

| SLLI rd, rs1, shamt |

Εγώ |

Μετατόπιση αριστερά λογικά αμέσως | rdß rs1 << shamt |

| SRLI rd, rs1, shamt |

Εγώ |

Άμεση μετατόπιση λογικής δεξιά | rdß rs1 >> shamt |

| SRAI rd, rs1, shamt |

Εγώ |

Άμεση μετατόπιση αριθμητικής προς τα δεξιά | rdß rs1 >> shamt |

Λειτουργίες φόρτωσης/καταστήματος

Οι λειτουργίες φόρτωσης/αποθήκευσης RISC V παρατίθενται παρακάτω.

| Μνημονικός | Τύπος | Εντολή | Περιγραφή |

| LD rd, imm12 (rs1) |

Εγώ |

Φόρτωση διπλής λέξης | rdß mem [rs1 +imm12] |

| LW rd, imm12 (rs1) |

Εγώ |

Φόρτωση λέξης | rdß mem [rs1 +imm12] |

| LH rd, imm12 (rs1) |

Εγώ |

Φορτώστε μέχρι τη μέση | rdß mem [rs1 +imm12] |

| LB rd, imm12 (rs1) |

Εγώ |

Φόρτωση byte | rdß mem [rs1 +imm12] |

| LWU rd, imm12 (rs1) |

Εγώ |

Φόρτωση λέξης χωρίς υπογραφή | rdß mem [rs1 +imm12] |

| LHU rd, imm12 (rs1) |

Εγώ |

Φόρτωση μισής λέξης χωρίς υπογραφή | rdß mem [rs1 +imm12] |

| LBU rd, imm12 (rs1) |

Εγώ |

Φόρτωση byte χωρίς υπογραφή | rdß mem [rs1 +imm12] |

| SD rs2, imm12 (rs1) |

μικρό |

Αποθηκεύστε διπλή λέξη | rs2 σε mem [rs1 +imm12] |

| SW rs2, imm12 (rs1) |

μικρό |

Κατάστημα λέξης | rs2 (31:0) σε mem [rs1 +imm12] |

| SH rs2, imm12 (rs1) |

μικρό |

Αποθηκεύστε στη μέση | rs2 (15:0) σε mem [rs1 +imm12] |

| SB rs2, imm12 (rs1) |

μικρό |

Αποθήκευση byte | rs2 (15:0) σε mem [rs1 +imm12] |

| SRAI rd, rs1, shamt |

Εγώ |

Άμεση μετατόπιση αριθμητικής προς τα δεξιά | rs2 (7:0) σε mem [rs1 +imm12] |

Λειτουργίες Διακλάδωσης

Οι λειτουργίες διακλάδωσης RISC V παρατίθενται παρακάτω.

| Μνημονικός | Τύπος | Εντολή | Περιγραφή |

| BEQ rs1, rs2, imm12 |

SB |

Υποκατάστημα ίσο | Αν rs1== rs2 PC ß PC+imm12 |

| BNE rs1, rs2, imm12 |

SB |

Υποκατάστημα όχι ίσο | Αν rs1!= rs2 PC ß PC+imm12 |

| BGE rs1, rs2, imm12 |

SB |

Κλάδος μεγαλύτερος ή ίσος | Αν rs1>= rs2 PC ß PC+imm12 |

| BGEU rs1, rs2, imm12 |

SB |

Κλάδος μεγαλύτερος ή ίσος με ανυπόγραφο | Αν rs1>= rs2 PC ß PC+imm12 |

| BLT rs1, rs2, imm12 |

SB |

Υποκατάστημα λιγότερο από | Αν rs1< rs2 PC ß PC+imm12 |

| BLTU rs1, rs2, imm12 |

SB |

Υποκατάστημα μικρότερο από ανυπόγραφο | Αν rs1< rs2 PC ß PC+imm12 <<1 |

| JAL rd, im20 |

UJ |

Άλμα και Σύνδεση | rdßPC+4 PCß PC+imm20 |

| JALR rd, imm12(rs1) |

Εγώ |

Εγγραφή Jump and Link | rdßPC+4 PCß rs1+imm12 |

Πλεονεκτήματα

ο πλεονεκτήματα του RISC Επεξεργαστής V περιλαμβάνουν τα ακόλουθα.

- Χρησιμοποιώντας το RISCV, μπορούμε να εξοικονομήσουμε χρόνο ανάπτυξης, ανάπτυξη λογισμικού, επαλήθευση κ.λπ.

- Αυτός ο επεξεργαστής έχει πολλά πλεονεκτήματα, όπως η απλότητα, το άνοιγμα, η αρθρωτή δομή, η καθαρή σχεδίαση και η επεκτασιμότητα.

- Αυτό υποστηρίζεται από πολλούς μεταγλωττιστές γλωσσών όπως το GCC (GNU Compiler Collection), ένας μεταγλωττιστής ελεύθερου λογισμικού και μέσω του Linux OS .

- Αυτό μπορεί να χρησιμοποιηθεί από τις εταιρείες ελεύθερα λόγω χωρίς δικαιώματα, χωρίς τέλη αδειοδότησης και χωρίς συνδεδεμένες συμβολοσειρές.

- Ο επεξεργαστής RISC-V δεν περιλαμβάνει νέα ή καινοτόμα χαρακτηριστικά επειδή απλώς ακολουθεί τις καθιερωμένες αρχές του RISC.

- Παρόμοια με πολλά άλλα ISA, αυτή η προδιαγραφή επεξεργαστή ορίζει απλώς διάφορα επίπεδα συνόλων εντολών. Έτσι, αυτό περιέχει παραλλαγές 32 & 64 bit καθώς και επεκτάσεις για υποστήριξη για οδηγίες κινητής υποδιαστολής.

- Αυτά είναι δωρεάν, απλά, αρθρωτά, σταθερά κ.λπ.

Μειονεκτήματα

ο μειονεκτήματα του επεξεργαστή RISC V περιλαμβάνουν τα ακόλουθα.

- Οι σύνθετες οδηγίες χρησιμοποιούνται συχνά από μεταγλωττιστές και προγραμματιστές.

- Το o/p ενός RISC μπορεί να αλλάξει με βάση τον κώδικα όταν οι επόμενες εντολές εντός ενός βρόχου εξαρτώνται από την προηγούμενη εντολή για εκτέλεση.

- Αυτοί οι επεξεργαστές πρέπει να αποθηκεύουν μια ποικιλία εντολών γρήγορα, κάτι που απαιτεί ένα μεγάλο σύνολο μνήμης cache για να ανταποκρίνεται στην εντολή έγκαιρα.

- Τα πλήρη χαρακτηριστικά, οι δυνατότητες και τα οφέλη του RISC εξαρτώνται κυρίως από την αρχιτεκτονική.

Εφαρμογές

ο εφαρμογές του RISC V επεξεργαστή περιλαμβάνουν τα ακόλουθα.

- Το RISC-V χρησιμοποιείται σε ενσωματωμένα συστήματα, τεχνητή νοημοσύνη και μηχανική μάθηση.

- Αυτοί οι επεξεργαστές χρησιμοποιούνται σε εφαρμογές ενσωματωμένου συστήματος που βασίζονται σε υψηλές επιδόσεις.

- Αυτός ο επεξεργαστής είναι κατάλληλος για χρήση σε ορισμένα συγκεκριμένα πεδία όπως υπολογιστές άκρων, τεχνητή νοημοσύνη και εφαρμογές αποθήκευσης.

- Το RISC-V είναι σημαντικό καθώς επιτρέπει σε μικρότερους κατασκευαστές συσκευών να σχεδιάζουν υλικό χωρίς να πληρώνουν.

- Αυτός ο επεξεργαστής επιτρέπει απλώς στους ερευνητές και τους προγραμματιστές να σχεδιάζουν καθώς και να ερευνούν με μια ελεύθερα διαθέσιμη αρχιτεκτονική ISA ή σετ εντολών.

- Οι εφαρμογές του RISC V κυμαίνονται από μικρούς ενσωματωμένους μικροελεγκτές έως επιτραπέζιους υπολογιστές και υπερυπολογιστές, συμπεριλαμβανομένων των διανυσματικών επεξεργαστών.

Έτσι, αυτό είναι μια επισκόπηση ενός επεξεργαστή RISC V – αρχιτεκτονική, εργασία με εφαρμογές. Εδώ είναι μια ερώτηση για εσάς, τι είναι ένας επεξεργαστής CISC;